Overview of the Cisco Nexus 3550-T Switches

The Cisco Nexus 3550-T Programmable Switch Platform is a powerful top-of-rack Ethernet switch and application platform with a unique low-latency design. It offers comprehensive layer 2 and layer 3 switching capabilities. The device is built around a flexible FPGA device, offering long term feature enhancements, upgrades, and fixes, as well as a complete firmware development environment for custom applications.

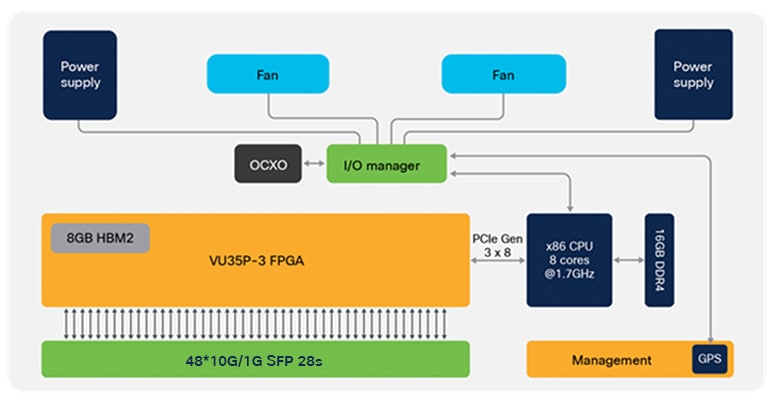

The hardware platform specifications of the Nexus 3550-T are as follows:

-

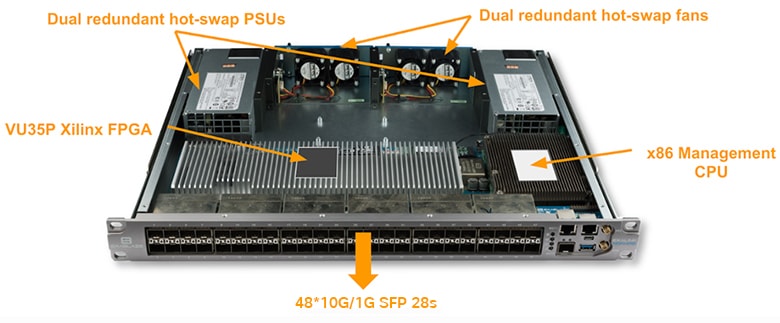

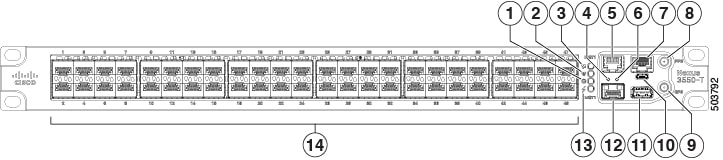

1RU 48 port SFP28 (Small Form-factor Pluggable 28) configuration (backwards compatible with SFP+ and SFP).

-

Dual redundant, hot-swap PSUs and dual hot-swap fans.

-

Build using a Xilinx Virtex Ultrascale Plus VU35P Field Programmable Gate Array (FPGA) with a “-3” speed grade. The chip has 8GB of High Bandwidth Memory (HBM) on board.

-

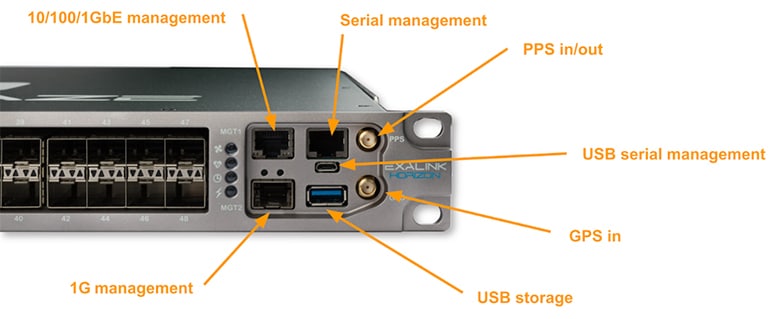

x86-based management processor with 100MB/s/1GB/s (RJ45) and 1GB (SFP+) based management ports.

-

Hardware (electronics) supporting 25G speeds to the FPGA.

The Cisco Nexus 3550-T Programmable Network Platform features a console port, a Micro USB port, and a 1G RJ45 port, which can be used as management interfaces. The Cisco Nexus 3550-T Platform uses a Command Line Interface (CLI) designed to address the needs of low-latency FPGA configurations.

The Cisco Nexus 3550-T Programmable Network Platform includes standard enterprise manageability and deployment capability features such as automatic configuration (via DHCP), SNMP, TACACS+ authentication, on-board Python programmability, BASH shell access, and time-series logging.

Please refer https://www.cisco.com/c/en/us/td/docs/dcn/nexus3550/3550-t/sw/101x/configuration/cisco-nexus-3550t-configuration-guide.html to learn more.

Feedback

Feedback