サーバ BIOS 設定

Cisco UCS では、Cisco UCS ドメイン 内のサーバ上の BIOS 設定をグローバルに変更する方法が 2 つ用意されています。サーバまたはサーバの集合のニーズに合う特定の BIOS 設定グループを含む BIOS ポリシーを 1 つ以上作成するか、特定のサーバ プラットフォームに対するデフォルトの BIOS 設定を使用できます。

BIOS ポリシーおよびサーバ プラットフォームのデフォルトの BIOS 設定のどちらででも、Cisco UCS Manager によって管理されるサーバの BIOS 設定を微調整できます。

データセンターのニーズに応じて、一部のサービス プロファイルについては BIOS ポリシーを設定し、同じ Cisco UCS ドメイン 内の他のサービス プロファイルについては BIOS のデフォルトを使用したり、そのいずれかのみを使用したりできます。また、Cisco UCS Manager を使用して、サーバの実際の BIOS 設定を表示し、それらが現在のニーズを満たしているかどうかを確認できます。

(注) |

Cisco UCS Manager は、BIOS ポリシーまたはデフォルトの BIOS 設定による BIOS 設定の変更を Cisco Integrated Management Controller(CIMC)バッファにプッシュします。これらの変更はバッファ内にとどまり、サーバがリブートされるまでは有効になりません。 設定するサーバで BIOS 設定のサポートを確認することをお勧めします。RAS メモリのミラーリング モードなどの一部の設定は、すべての Cisco UCS サーバでサポートされているわけではありません。 |

メイン BIOS 設定

次の表は、BIOS ポリシーまたはデフォルトの BIOS 設定を介して行うことができるメイン サーバの BIOS 設定を示しています。

| 名前 | 説明 |

|---|---|

|

Properties |

|

|

[Reboot on BIOS Settings Change] |

1 つ以上の BIOS 設定を変更した後、サーバをリブートするタイミング。 この設定を有効にした場合、サーバのサービス プロファイルのメンテナンス ポリシーに従ってサーバがリブートされます。たとえば、メンテナンス ポリシーでユーザの確認応答が必要な場合、サーバはリブートされず、ユーザが保留中のアクティビティを確認するまで BIOS の変更は適用されません。 この設定を有効にしない場合、BIOS の変更は、別のサーバ設定変更の結果であれ手動リブートであれ、次回のサーバのリブート時まで適用されません。 |

|

BIOS 設定 |

|

|

[Quiet Boot] |

BIOS が Power On Self-Test(POST)中に表示する内容。次のいずれかになります。

|

|

[POST error pause] |

POST 中にサーバで重大なエラーが発生した場合の処理。次のいずれかになります。

|

|

[Resume on AC power loss] |

予期しない電力損失後に電力が復帰したときにサーバがどのように動作するかを決定します。次のいずれかになります。

|

|

[Front panel lockout] |

前面パネルの電源ボタンとリセット ボタンがサーバによって無視されるかどうかを決定します。次のいずれかになります。

|

|

[CDN Control] |

一貫したデバイスの命名によって、一貫した方法でイーサネット インターフェイスに名前を付けることができます。これによりイーサネット インターフェイスの名前は、より統一され、識別しやすくなり、アダプタや他の設定に変更が加えられても永続的に保持されます。 一貫したデバイスの命名をイネーブルにするかどうか。次のいずれかになります。

|

プロセッサの BIOS 設定

次の表は、BIOS ポリシーまたはデフォルトの BIOS 設定を介して行うことができるプロセッサの BIOS 設定を示しています。

| 名前 | 説明 | ||

|---|---|---|---|

|

[Intel Turbo Boost Tech] |

プロセッサで Intel Turbo Boost Technology を使用するかどうか。このテクノロジーでは、仕様よりも低い電力、温度、または電圧でプロセッサが動作していると、自動的にそのプロセッサの周波数が上がります。次のいずれかになります。

|

||

|

[Enhanced Intel SpeedStep Tech] |

プロセッサで Enhanced Intel SpeedStep Technology を使用するかどうか。このテクノロジーでは、プロセッサの電圧やコア周波数をシステムが動的に調整できます。このテクノロジーにより、平均電力消費量と平均熱発生量が減少する可能性があります。次のいずれかになります。

オペレーティング システムがこの機能をサポートするかどうかについては、オペレーティング システムのベンダーに問い合わせることを推奨します。 |

||

|

[Intel HyperThreading Tech] |

プロセッサで Intel Hyper-Threading Technology を使用するかどうか。このテクノロジーでは、マルチスレッド ソフトウェア アプリケーションのスレッドを各プロセッサ内で並列に実行できます。次のいずれかになります。

オペレーティング システムがこの機能をサポートするかどうかについては、オペレーティング システムのベンダーに問い合わせることを推奨します。 |

||

|

[コア多重処理(Core Multi Processing)] |

パッケージ内の CPU ごとの論理プロセッサ コアの状態を設定します。この設定を無効にした場合は、Intel Hyper Threading Technology も無効になります。次のいずれかになります。

オペレーティング システムがこの機能をサポートするかどうかについては、オペレーティング システムのベンダーに問い合わせることを推奨します。 |

||

|

[Execute Disable Bit] |

サーバのメモリ領域を分類し、アプリケーション コードを実行可能な場所を指定します。この分類の結果、悪意のあるワームがバッファにコードを挿入しようとした場合、プロセッサでコードの実行をディセーブルにします。この設定は、損害、ワームの増殖、および特定クラスの悪意のあるバッファ オーバーフロー攻撃を防止するのに役立ちます。次のいずれかになります。

オペレーティング システムがこの機能をサポートするかどうかについては、オペレーティング システムのベンダーに問い合わせることを推奨します。 |

||

|

[Intel Virtualization Technology] |

プロセッサで Intel Virtualization Technology を使用するかどうか。このテクノロジーでは、1 つのプラットフォームで、複数のオペレーティング システムとアプリケーションをそれぞれ独立したパーティション内で実行できます。次のいずれかになります。

|

||

|

[Hardware Prefetcher] |

プロセッサで、インテル ハードウェア プリフェッチャが必要に応じてデータおよび命令ストリームをメモリから取得し、統合 2 次キャッシュに入れることを許可するかどうか。次のいずれかになります。

|

||

|

[Adjacent Cache Line Prefetcher] |

プロセッサで必要な行のみを取得するのではなく、偶数または奇数のペアのキャッシュ行を取得するかどうか。次のいずれかになります。

|

||

|

[DCU Streamer Prefetch] |

プロセッサで DCU IP Prefetch メカニズムを使用して履歴キャッシュ アクセス パターンを分析し、L1 キャッシュ内で最も関連性の高い行をプリロードします。次のいずれかになります。

|

||

|

[DCU IP Prefetcher] |

プロセッサで DCU IP Prefetch メカニズムを使用して履歴キャッシュ アクセス パターンを分析し、L1 キャッシュ内で最も関連性の高い行をプリロードします。次のいずれかになります。

|

||

|

[KTI Prefetch] ドロップダウン リスト |

KTI プリフェッチは、DDR バス上でメモリ読み込みが早期に開始されるようにするメカニズムです。これは次のいずれかになります。

|

||

|

[LLC Prefetch] ドロップダウン リスト |

プロセッサが LLC プリフェッチ メカニズムを使用して日付を LLC にフェッチするかどうか。次のいずれかになります。

|

||

|

[XPT Prefetch] ドロップダウン リスト |

XPT プリフェッチを使用して、最後のレベルのキャッシュに読み取り要求を送信できるようにして、その要求のコピーをメモリ コントローラのプリフェッチャに発行するかどうか。次のいずれかになります。

|

||

|

[Direct Cache Access] |

プロセッサで、データを I/O デバイスから直接プロセッサ キャッシュに入れることにより、I/O パフォーマンスを向上させることができます。この設定はキャッシュ ミスを減らすのに役立ちます。次のいずれかになります。

|

||

|

[Processor C State] |

アイドル期間中にシステムが省電力モードに入ることができるかどうか。次のいずれかになります。

オペレーティング システムがこの機能をサポートするかどうかについては、オペレーティング システムのベンダーに問い合わせることを推奨します。 |

||

|

[Processor C1E] |

C1 に入ってプロセッサが最低周波数に遷移できるようにします。この設定は、サーバをリブートするまで有効になりません。次のいずれかになります。

|

||

|

[Processor C3 Report] |

プロセッサからオペレーティング システムに C3 レポートを送信するかどうか。次のいずれかになります。

Cisco UCS B440 Server の場合、[BIOS Setup] メニューでこれらのオプションに対して [enabled] と [disabled] が使用されます。[acpi-c2] または [acpi-c2] を指定すると、このサーバではそのオプションの BIOS 値に [enabled] が設定されます。 |

||

|

[Processor C6 Report] |

プロセッサからオペレーティング システムに C6 レポートを送信するかどうか。次のいずれかになります。

|

||

|

[Processor C7 Report] ドロップダウン リスト |

プロセッサからオペレーティング システムに C7 レポートを送信するかどうか。次のいずれかになります。

|

||

|

[Processor CMCI] ドロップダウン リスト |

CMCI の生成を有効にします。次のいずれかになります。

|

||

|

[CPU Performance] |

サーバの CPU パフォーマンス プロファイルを設定します。次のいずれかになります。

|

||

|

[Max Variable MTRR Setting] |

平均修復時間(MTRR)変数の数を選択できます。次のいずれかになります。

|

||

|

[Local X2 APIC] |

Application Policy Infrastructure Controller(APIC)アーキテクチャ タイプを設定できます。次のいずれかになります。

|

||

|

[Power Technology] |

次のオプションの CPU 電源管理設定を指定できます。

[Power Technology] は次のいずれかになります。

|

||

|

[Energy Performance] |

システム パフォーマンスまたはエネルギー効率がこのサーバで重要かどうかを判断できます。次のいずれかになります。

|

||

|

[Frequency Floor Override] |

アイドル時に、CPU がターボを除く最大周波数よりも低い周波数にできるようにするかどうか。次のいずれかになります。

|

||

|

[P STATE Coordination] |

BIOS がオペレーティング システムに P-state サポート モデルを伝達する方法を定義できます。Advanced Configuration and Power Interface(ACPI)仕様では、次の 3 つのモデルが定義されています。

|

||

|

[DRAM Clock Throttling] |

メモリ帯域幅と消費電力に関してシステム設定を調整できます。次のいずれかになります。

|

||

|

[Channel Interleaving] |

CPU がメモリ ブロックを分割して、インターリーブされたチャネル間にデータの連続部分を分散し、同時読み取り動作を有効にするかどうか。次のいずれかになります。

|

||

|

[Rank Interleaving]ドロップダウン リスト |

1 つのランクを更新中に別のランクにアクセスできるよう、CPU がメモリの物理ランクをインターリーブするかどうか。次のいずれかになります。

|

||

|

[Sub NUMA Clustering] ドロップダウンリスト |

CPU がサブ NUMA クラスタリングをサポートするかどうか。そのクラスタリングでは、タグ ディレクトリとメモリ チャネルは常に同じ領域にあります。次のいずれかになります。

|

||

|

[IMC Interleave] ドロップダウン リスト |

この BIOS オプションは、Integrated Memory Controller(IMC)間のインターリーブを制御します。

|

||

|

[Memory Interleaving] |

メモリの更新中に別のメモリにアクセスできるように、CPU が物理メモリをインターリーブするかどうか。次のいずれかになります。

|

||

|

[Demand Scrub] |

CPU または I/O から読み取り要求があった時に発生したシングル ビット メモリ エラーを、システムで修正するかどうか。次のいずれかになります。

|

||

|

[Patrol Scrub] |

システムがサーバ上のメモリの未使用部分でも単一ビット メモリ エラーをアクティブに探して訂正するかどうか。次のいずれかになります。

|

||

|

[Altitude] |

物理サーバがインストールされている地点のおよその海抜(m 単位)。次のいずれかになります。

|

||

|

[Package C State Limit] |

アイドル時にサーバ コンポーネントが使用できる電力量。次のいずれかになります。

|

||

|

[CPU Hardware Power Management] ドロップダウンリスト |

プロセッサの Hardware Power Management(HWPM)をイネーブルにします。次のいずれかになります。

|

||

|

[Energy Performance Tuning] ドロップダウン リスト |

BIOS または OS によってエネルギー パフォーマンスのバイアス調整をオンにできるかどうかを指定します。オプションは [BIOS] と [OS] です。

|

||

|

[Workload Configuration] ドロップダウン リスト |

この機能を使用すると、ワークロードを最適化できます。オプションは [Balanced] と [I/O Sensitive] です。

|

||

|

[Core Performance Boost] ドロップダウンリスト |

AMD プロセッサがアイドル状態(ほとんど使用されていない状態)のときにコアの周波数を上げるかどうかを指定します。次のいずれかになります。

|

||

|

[Global C-state Control] ドロップダウンリスト |

AMD プロセッサが IO ベースの C ステートおよび DF C ステートを制御するかどうかに関係なく、これは次のうちいずれかになります。

|

||

|

[L1 Stream HW Prefetcher] ドロップダウンリスト |

プロセッサで、AMD ハードウェア プリフェッチャが必要に応じてデータおよび命令ストリームをメモリから取得し、L1 キャッシュに入れることを許可するかどうか。次のいずれかになります。

|

||

|

[L2 Stream HW Prefetcher] ドロップダウンリスト |

プロセッサで、AMD ハードウェア プリフェッチャが必要に応じてメモリからデータおよび命令ストリームを取得し、L2 キャッシュに入れることを許可するかどうかを指定します。次のいずれかになります。

|

||

|

[AMD Memory Interleaving] ドロップダウンリスト |

物理メモリの更新中に別のメモリにアクセスできるよう、AMD CPU がメモリをインターリーブするかどうかを指定します。このオプションは、ファブリック レベルでメモリのインターリーブを制御します。チャネル、ダイ、ソケットの要件はメモリによって異なるため、選択したオプションがメモリでサポートされない場合これらは無視されます。次のいずれかを選択できます。

|

||

|

[AMD Memory Interleaving Size] ドロップダウンリスト |

インターリーブされるメモリ ブロックのサイズを決定します。また、インターリーブの開始アドレス(ビット 8、9、10、11)も指定します。次のいずれかになります。

|

||

|

[Chipselect Interleaving] ドロップダウンリスト |

ノード 0 に選択する DRAM チップ経由でメモリ ブロックがインターリーブされるかどうか。次のいずれかになります。

|

||

|

[Bank Group Swap] ドロップダウンリスト |

物理アドレスをアプリケーションに割り当てる方法を決定します。次のいずれかになります。

|

||

|

[Determinism Slider] ドロップダウンリスト |

AMD プロセッサにより動作方法を決定できます。次のいずれかになります。

|

||

|

[IOMMU] ドロップダウンリスト |

出入力メモリ管理ユニット(IOMMU) により、AMD プロセッサが物理アドレスへ仮想アドレスをマッピングすることが可能です。次のいずれかになります。

|

||

|

[Downcore control] ドロップダウンリスト |

AMD プロセッサ コアを無効にしているため、有効にするコアの数を選択できます。次のいずれかになります。

|

||

|

[SVM Mode] ドロップダウンリスト |

プロセッサが AMD セキュア仮想マシン テクノロジを使用するかどうか。次のいずれかを選択できます。

|

||

|

[SMT Mode] ドロップダウンリスト |

プロセッサで AMD Simultaneous MultiThreading テクノロジーを使用するかどうかを指定します。このテクノロジーでは、マルチスレッド ソフトウェア アプリケーションのスレッドを各プロセッサ内で並列に実行できます。次のいずれかになります。

|

||

|

[SMEE] ドロップダウンリスト |

プロセッサで、メモリの暗号化サポートを実現する Secure Memory Encryption Enable(SMEE)機能を使用するかどうかを指定します。次のいずれかになります。

|

Intel Directed I/O の BIOS 設定

次の表は、BIOS ポリシーまたはデフォルトの BIOS 設定を介して行うことができる Intel Directed I/O の BIOS 設定を示しています。

| 名前 | 説明 | ||

|---|---|---|---|

|

[Intel VT for Directed IO] |

Intel Virtualization Technology for Directed I/O(VT-d)をプロセッサで使用するかどうか。次のいずれかになります。

|

||

|

[Intel VTD interrupt Remapping] |

プロセッサで Intel VT-d Interrupt Remapping をサポートするかどうか。次のいずれかになります。

|

||

|

[Intel VTD coherency support] |

プロセッサで Intel VT-d Coherency をサポートするかどうか。次のいずれかになります。

|

||

|

[Intel VTD ATS support] |

プロセッサで Intel VT-d Address Translation Services(ATS)をサポートするかどうか。次のいずれかになります。

|

||

|

[Intel VTD pass through DMA support] |

プロセッサで Intel VT-d Pass-through DMA をサポートするかどうか。次のいずれかになります。

|

RAS メモリの BIOS 設定

次の表に、BIOS ポリシーまたはデフォルト BIOS 設定を介して実行できる RAS メモリの BIOS 設定の一覧を示します。

| 名前 | 説明 |

|---|---|

|

[Memory RAS configuration] |

サーバに対するメモリの Reliability, Availability, and Serviceability(RAS)の設定方法。次のいずれかになります。

|

|

[NUMA optimized] |

BIOS で NUMA をサポートするかどうか。次のいずれかになります。

|

|

[Mirroring Mode] |

メモリのミラーリングでは、メモリに 2 つの同じデータ イメージを保存することにより、システムの信頼性が向上します。 このオプションは、[Memory RAS Config] で [mirroring] オプションを選択したときのみ使用可能です。次のいずれかを指定できます。

|

|

[Sparing Mode] |

スペアリングはメモリを予備に保持することで信頼性を最適化し、別の DIMM の障害発生時に使用できるようにします。このオプションは、メモリの冗長性を実現しますが、ミラーリングほどの冗長性は提供されません。使用可能なスペアリングのモードは、現在のメモリの数によって異なります。 このオプションは、[Memory RAS Config] で [sparing] オプションを選択したときのみ使用可能です。次のいずれかを指定できます。

|

|

[LV DDR Mode] |

低電圧と高周波数のどちらのメモリ動作をシステムで優先するか。次のいずれかになります。

|

|

[DRAM Refresh Rate] set dram-refresh-rate-config dram-refresh |

内部メモリ用の更新間隔レート。次のいずれかになります。

|

|

[DDR3 Voltage Selection] |

デュアル電圧 RAM に使用される電圧。次のいずれかになります。

|

シリアル ポートの BIOS 設定

次の表に、BIOS ポリシーまたはデフォルト BIOS 設定を介して実行できるシリアル ポートの BIOS 設定の一覧を示します。

| 名前 | 説明 |

|---|---|

|

[Serial port A enable] |

シリアル ポート A がイネーブルかディセーブルか。次のいずれかになります。

|

USB の BIOS 設定

次の表に、BIOS ポリシーまたはデフォルト BIOS 設定を介して実行できる USB BIOS 設定の一覧を示します。

| 名前 | 説明 |

|---|---|

|

[Make Device Non Bootable] |

サーバが USB デバイスからブートできるかどうか。次のいずれかになります。

|

|

[Legacy USB Support] |

システムでレガシー USB デバイスをサポートするかどうか。次のいずれかになります。

|

|

[USB Idle Power Optimizing Setting] |

USB EHCI のアイドル時電力消費を減らすために USB アイドル時電力最適化設定を使用するかどうか。この設定で選択した値によって、パフォーマンスが影響を受けることがあります。次のいずれかになります。

|

|

[USB Front Panel Access Lock] |

USB 前面パネル アクセス ロックは、USB ポートへの前面パネル アクセスをイネーブルまたはディセーブルにするために設定されます。次のいずれかになります。

|

|

[Port 60/64 Emulation] |

完全な USB キーボード レガシー サポートのために 60h/64h エミュレーションをシステムでサポートするかどうか。次のいずれかになります。

|

|

[USB Port Front] |

前面パネルの USB デバイスがイネーブルかディセーブルか。次のいずれかになります。

|

|

[USB Port Internal] |

内部 USB デバイスがイネーブルかディセーブルか。次のいずれかになります。

|

|

[USB Port KVM] |

KVM ポートがイネーブルかディセーブルか。次のいずれかになります。

|

|

[USB Port Rear] |

背面パネルの USB デバイスがイネーブルかディセーブルか。次のいずれかになります。

|

|

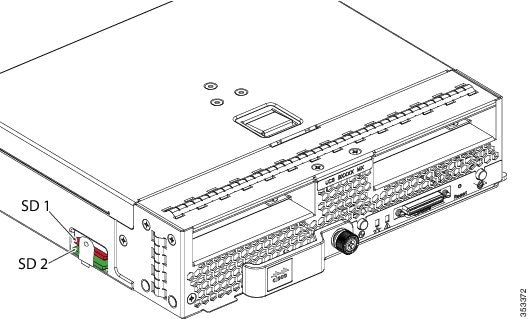

[USB Port SD Card] |

SD カード ドライブがイネーブルかディセーブルか。次のいずれかになります。

|

|

[USB Port VMedia] |

仮想メディア デバイスがイネーブルかディセーブルか。次のいずれかになります。

|

|

[All USB Devices] |

すべての物理および仮想 USB デバイスがイネーブルであるか、ディセーブルであるか。次のいずれかになります。

|

|

[xHCI Mode] |

xHCI モードを有効または無効にします。次のいずれかになります。

|

PCI 設定の BIOS 設定

次の表は、BIOS ポリシーまたはデフォルトの BIOS 設定を介して行うことができる PCI 設定の BIOS 設定を示しています。

| 名前 | 説明 | ||||

|---|---|---|---|---|---|

|

[Maximum memory below 4GB] |

PAE サポートなしで動作しているオペレーティング システムのメモリ使用率を、BIOS がシステム設定に応じて 4GB 以下で最大化するかどうか。次のいずれかになります。

|

||||

|

[Memory mapped IO above 4GB] |

64 ビット PCI デバイスの 4 GB 以上のアドレス空間に対するメモリ マップド I/O をイネーブルにするか、ディセーブルにするか。レガシーなオプション ROM は 4 GB を超えるアドレスにアクセスできません。PCI デバイスが 64 ビット対応でも、レガシーなオプション ROM を使用する場合は、この設定をイネーブルにしても正しく機能しない場合があります。次のいずれかになります。

|

||||

|

[VGA Priority] |

システムに複数の VGA デバイスがある場合は、VGA グラフィックス デバイスのプライオリティを設定できます。次のいずれかになります。

|

||||

|

[ASPM Support] |

BIOS での ASPM(アクティブ電源状態管理)サポートのレベルを設定できます。次のいずれかになります。

|

||||

|

[BME DMA Mitigation Support] |

不正な外部 DMA からの脅威を緩和する PCI BME ビットを無効にできます。次のいずれかになります。

|

QPI の BIOS 設定

次の表は、BIOS ポリシーまたはデフォルトの BIOS 設定を介して行うことができる QPI の BIOS 設定を示しています。

| 名前 | 説明 |

|---|---|

|

[QPI Link Frequency Select] |

Intel QuickPath Interconnect(QPI)リンク周波数(ギガトランスファー/秒(MT/s)単位)。次のいずれかになります。

|

|

[QPI Snoop Mode] |

次のいずれかになります。

|

LOM および PCIe スロットの BIOS 設定

次の表に、BIOS ポリシーまたはデフォルト BIOS 設定を介して実行できる USB BIOS 設定の一覧を示します。

| 名前 | 説明 |

|---|---|

|

[PCIe Slot SAS OptionROM] |

オプション ROM が SAS ポートで使用できるかどうか。次のいずれかになります。

|

|

[PCIe Slot n Link Speed] |

このオプションを使用すると、PCIe スロット n に装着されているアダプタ カードの最大速度を制限できます。次のいずれかになります。

|

|

[PCIe Slot n OptionROM] |

オプション ROM がポートで使用できるかどうか。次のいずれかになります。

|

|

[PCIe Slot HBA OptionROM] |

オプション ROM が HBA ポートで使用できるかどうか。次のいずれかになります。

|

|

[PCIe Slot MLOM OptionROM] |

オプション ROM が MLOM ポートで使用できるかどうか。次のいずれかになります。

|

|

[PCIe Slot Nx OptionROM] |

オプション ROM がポートで使用できるかどうか。次のいずれかになります。

|

|

[PCIe 10G LOM 2 Link] |

オプション ROM が 10G LOM ポートで使用できるかどうか。次のいずれかになります。

|

|

PCI ROM CLP |

PCI ROM Command Line Protocol(CLP)は、カード上の iSCSI や PxE などのさまざまなオプション ROM の実行を制御します。デフォルト設定は、ディセーブルです。

|

|

SIOC1 Option ROM |

システム I/O コントローラ 1(SIOC1)のオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

SIOC2 Option ROM |

システム IO コントローラ 2(SIOC2)にあるオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

SBMEZZ1 Option ROM |

SBMezz1 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

SBMEZZ2 Option ROM |

SBMezz2 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

IOESlot1 OptionROM |

オプション ROM が IOE スロット 1 で有効かどうか。次のいずれかになります。

|

|

IOEMEZZ 1 OptionROM |

オプション ROM が IOE Mezz1 で有効かどうか。次のいずれかになります。

|

|

IOE Slot2 Option ROM |

オプション ROM が IOE スロット 2 で有効かどうか。次のいずれかになります。

|

|

IO ENVME1 Option ROM |

オプション ROM が IOE NVMe1 で有効かどうか。次のいずれかになります。

|

|

IO ENVME2 Option ROM |

オプション ROM が IOE NVMe2 で有効かどうか。次のいずれかになります。

|

|

SBNVME1 Option ROM |

SBNVMe1 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

[PCIe Slot MRAID OptionROM] ドロップダウン リスト |

オプション ROM が MRAID ポートで使用できるかどうか。次のいずれかになります。

|

|

PCIe Slot RAID OptionROM |

オプション ROM が RAID ポートで使用できるかどうか。次のいずれかになります。

|

|

PCIe Slot Rear Nvmen OptionRom |

オプション ROM が背面 NVMEn ポートで使用できるかどうか。次のいずれかになります。

|

|

Rear NVME1 Link Speed |

このオプションを使用すると、背面 PCIe スロット 1 に取り付けられた NVME カードの最大速度を制限できます。次のいずれかになります。

|

|

Rear NVME2 Link Speed |

このオプションを使用すると、背面 PCIe スロット 2 に取り付けられた NVME カードの最大速度を制限できます。次のいずれかになります。

|

|

Front NVME1 Link Speed |

このオプションでは、前面 PCIe スロット 1 に取り付けられた NVME カードの最高速度を制限することができます。次のいずれかになります。

|

|

Front NVME2 Link Speed |

このオプションでは、前面 PCIe スロット 2 に取り付けられた NVME カードの最高速度を制限することができます。次のいずれかになります。

|

|

HBA Link Speed |

このオプションでは、HBA カードの最高速度を制限することができます。次のいずれかになります。

|

|

MLOM Link Speed |

このオプションを使用すると MLOM アダプタの最大速度を制限できます。次のいずれかになります。

|

|

MRAID Link Speed |

このオプションでは、MRAID の最高速度を制限することができます。次のいずれかになります。

|

|

RAID Link Speed |

このオプションを使用すると RAID の最大速度を制限できます。次のいずれかになります。

|

|

All Onboard LOM |

すべてのオンボード LOM ポートがイネーブルであるか、ディセーブルであるか。次のいずれかになります。

|

|

LOM Port 1 OptionRom |

オプション ROM が LOM ポート 1 で使用できるかどうか。次のいずれかになります。

|

|

LOM Port 2 OptionRom |

オプション ROM が LOM ポート 2 で使用できるかどうか。次のいずれかになります。

|

|

[Slot n State] |

PCIe スロット n に取り付けられているアダプタ カードの状態。次のいずれかになります。

|

|

[SBNVMe1 OptionROM] |

SBNVMe1 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

[SBNVMe2 OptionROM] |

SBNVMe2 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

[SIOCNVMe1 OptionROM] リスト |

SIOCNVMe1 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

[SIOCNVMe2 OptionROM] |

SIOCNVMe2 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

[SBLom1 OptionROM] |

SBLom1 コントローラのオプション ROM をサーバが使用できるかどうか。次のいずれかになります。

|

|

[SBNVMen Link Speed] |

SBNVMe スロット n のリンク速度。次のいずれかになります。

|

|

[SIOCNVMen Link Speed] |

SIOCNVMe スロット n のリンク速度。次のいずれかになります。

|

|

[SIOCn Link Speed] |

SIOC スロット n のリンク速度。次のいずれかになります。

|

|

[SBMezzn Link Speed] |

SBMezz スロット n のリンク速度。次のいずれかになります。

|

|

[IOESlotn Link Speed] |

IOE スロット n のリンク速度。次のいずれかになります。

|

|

[IOEMezzn Link Speed] |

IOEMezz スロット n のリンク速度。次のいずれかになります。

|

|

[IOENVMen Link Speed] |

IOENVMe スロット n のリンク速度。次のいずれかになります。

|

|

[CDN Support for LOMs] |

イーサネット ネットワーキング識別子の命名規則を、Consistent Device Naming(CDN)と従来の命名規則のどちらに準拠させるかを指定します。次のいずれかになります。

|

|

[VMD Enable] |

PCIe バスに接続されている NVMe SSD をスワップできるかどうかを指定します。この設定により、これらのドライブの LED ステータス ライトも標準化されます。次のいずれかになります。

|

|

PCIe Slot GPUn OptionROM ドロップダウン リスト 次の場合のみ Cisco UCS C480 M5 ML Server |

GPU スロットnのオプション ROM が有効かどうか。nは、1 ~ 8 のスロット番号です。次のいずれかになります。

|

グラフィックス構成の BIOS 設定

次の表に、BIOS ポリシーまたはデフォルトの BIOS 設定を介して実行できるグラフィックス構成の BIOS 設定の一覧を示します。

| 名前 | 説明 |

|---|---|

|

[Integrated Graphics] |

統合グラフィックスをイネーブルにします。次のいずれかになります。

|

|

Integrated Graphics Aperture Size |

統合グラフィックス コントローラのマップド メモリのサイズを設定できます。次のいずれかになります。

|

|

Onboard Graphics |

オンボード グラフィックス(KVM)をイネーブルにします。次のいずれかになります。

|

Boot Options BIOS Settings

The following table lists the boot options BIOS settings that you can configure through a BIOS policy or the default BIOS settings:

| Name | Description |

|---|---|

|

Boot option retry |

Whether the BIOS retries NON-EFI based boot options without waiting for user input. This can be one of the following:

|

|

SAS RAID |

Whether the Intel SAS Entry RAID Module is enabled. This can be one of the following:

|

|

SAS RAID module |

How the Intel SAS Entry RAID Module is configured. This can be one of the following:

|

|

Onboard SCU Storage Support |

Whether the onboard software RAID controller is available to the server. This can be one of the following:

|

|

Cool Down Time (sec) drop-down list |

The time to wait (in seconds) before the next boot attempt. This can be one of the foliwibng This token is valid only when the Boot Option Retry token has been enabled.

|

|

Number of Retries drop-down list |

Number of attempts to boot. This can be one of the following:

|

|

P-SATA mode drop-down list |

This options allows you to select the P-SATA mode. This can be one of the following:

|

|

Power On Password drop-down list |

This token requires that you set a BIOS password before using the F2 BIOS configuration. If enabled, password needs to be validated before you access BIOS functions such as IO configuration, BIOS set up, and booting to an operating system using BIOS. It can be one of the following:

|

|

IPV6 PXE Support drop-down list |

Enables or disables IPV6 support for PXE. This can be one of the following

|

|

Adaptive Memory Training drop-down list |

When this token is enabled, the BIOS saves the memory training results (optimized timing/voltage values) along with CPU/memory configuration information and reuses them on subsequent reboots to save boot time. The saved memory training results are used only if the reboot happens within 24 hours of the last save operation. This can be one of the following:

|

|

BIOS Techlog Level BIOS Tech Message Level Control (for C125 M5) |

Enabling this token allows the BIOS Tech log output to be controlled at more a granular level. This reduces the number of BIOS Tech log messages that are redundant, or of little use. This can be one of the following:

|

|

OptionROM Launch Optimization |

The Option ROM launch is controlled at the PCI Slot level, and is enabled by default. In configurations that consist of a large number of network controllers and storage HBAs having Option ROMs, all the Option ROMs may get launched if the PCI Slot Option ROM Control is enabled for all. However, only a subset of controllers may be used in the boot process. When this token is enabled, Option ROMs are launched only for those controllers that are present in boot policy. This can be one of the following:

|

(注) |

BIOS parameter virtualization capability in Cisco UCS Manager maps a unified set of BIOS settings in a service profile to the actual BIOS supporting parameters. However, not all BIOS setting items are applicable to every server model/platform. When you create a custom BIOS policy and have the Boot Option Retry selected, and when there is no bootable option available, the reboot fails on the Cisco UCS B420 M3 or Cisco UCS B420 M4 servers and Cisco UCS Manager displays this message : Reboot and Select proper Boot device or Insert Boot Media in selected Boot device and press a key. You must manually set a boot option after the boot path is corrected, in order to enable the servers to reboot after a power outage. For more information about BIOS default server policies and the BIOS options and their default settings, see BIOS ポリシー and サーバ BIOS 設定. |

サーバ管理 BIOS 設定

次の表に、BIOS ポリシーまたはデフォルト BIOS 設定を介して実行できるサーバ管理 BIOS 設定の一覧を示します。

General Settings

| 名前 | 説明 |

|---|---|

|

[Assert NMI on SERR] |

システム エラー(SERR)の発生時に、BIOS がマスク不能割り込み(NMI)を生成し、エラーをログに記録するかどうか。次のいずれかになります。

|

|

[Assert NMI on PERR] |

プロセッサ バス パリティ エラー(PERR)の発生時に、BIOS がマスク不能割り込み(NMI)を生成し、エラーをログに記録するかどうか。次のいずれかになります。

|

|

[OS Boot Watchdog Timer] |

BIOS が定義済みのタイム アウト値を持つウォッチドッグ タイマーをプログラムするかどうか。タイマーが切れる前にオペレーティング システムのブートを完了しない場合、CIMC はシステムをリセットし、エラーがログに記録されます。次のいずれかになります。

この機能には、オペレーティング システムのサポートまたは Intel 管理ソフトウェアが必要です。 |

|

[OS Boot Watchdog Timer Policy] |

ウォッチドッグ タイマーが切れた場合にシステムで実行されるアクション。次のいずれかになります。

このオプションは、[OS Boot Watchdog Timer] をイネーブルにした場合にだけ利用できます。 |

|

[OS Boot Watchdog Timer Timeout] |

BIOS でウォッチドッグ タイマーの設定に使用されるタイムアウト値。次のいずれかになります。

このオプションは、[OS Boot Watchdog Timer] をイネーブルにした場合にだけ利用できます。 |

|

[FRB-2 タイマー(FRB-2 Timer)] |

POST 中にシステムがハングした場合に、システムを回復するために FRB-2 タイマーが使用されるかどうか。次のいずれかになります。

|

コンソール リダイレクション設定

| 名前 | 説明 | ||

|---|---|---|---|

|

[Console redirection] |

POST および BIOS のブート中に、シリアル ポートをコンソール リダイレクションに使用できるようにします。BIOS のブートが完了し、オペレーティング システムがサーバを担当すると、コンソール リダイレクションは関連がなくなり、無効になります。次のいずれかになります。

|

||

|

[Flow Control] |

フロー制御にハンドシェイク プロトコルを使用するかどうか。送信要求/クリア ツー センド(RTS/CTS)を使用すると、隠れた端末問題が原因で発生する可能性があるフレーム コリジョンを減らすことができます。次のいずれかになります。

|

||

|

[Baud rate] |

シリアル ポートの伝送速度として使用されるボー レート。[Console Redirection] をディセーブルにした場合は、このオプションを使用できません。次のいずれかになります。

|

||

|

[Terminal type] |

コンソール リダイレクションに使用される文字フォーマットのタイプ。次のいずれかになります。

|

||

|

[Legacy OS redirection] |

シリアル ポートでレガシーなオペレーティング システム(DOS など)からのリダイレクションをイネーブルにするかどうか。次のいずれかになります。

|

||

|

[Putty KeyPad] set console-redir-config putty-function-keypad |

PuTTY ファンクション キーおよびテンキーの最上段のキーのアクションを変更できます。次のいずれかになります。

|

||

|

[Out of Band Management] ドロップダウンリスト |

Windows の Special Administration Control(SAC)で使用。このオプションを使用すると、Windows 緊急管理サービスに使用できる COM ポート 0 を設定できます。このセットアップ オプションに基づいて ACPI SPCR テーブルが報告されます。次のいずれかになります。

|

||

|

[Redirection After BIOS POST] ドロップダウン リスト set console-redir-config putty-function-keypad |

BIOS POST が完了し、OS ブートローダに制御が渡された後に、BIOS コンソール リダイレクションがアクティブであるかどうか。次のいずれかになります。

|

フィードバック

フィードバック