Cisco ONS 15454 のタイミングと同期

内容

概要

このドキュメントでは、Cisco ONS 15454 のタイミングと同期を計画する際のガイドラインを示します。

前提条件

要件

次の項目に関する知識があることが推奨されます。

-

Cisco ONS 15454

使用するコンポーネント

このドキュメントの情報は、次のソフトウェアとハードウェアのバージョンに基づいています。

-

Cisco ONS 15454

このドキュメントの情報は、特定のラボ環境にあるデバイスに基づいて作成されました。このドキュメントで使用するすべてのデバイスは、初期(デフォルト)設定の状態から起動しています。対象のネットワークが実稼働中である場合には、どのようなコマンドについても、その潜在的な影響について確実に理解しておく必要があります。

表記法

ドキュメント表記の詳細は、『シスコ テクニカル ティップスの表記法』を参照してください。

背景説明

この製品には次のものが含まれます。

-

American National Standards Institute/Synchronous Optical NETwork(ANSI/SONET)プロビジョニングプラットフォーム

-

欧州通信規格協会/国際電気通信連合/同期デジタル階層(ETSI/ITU/SDH)プロビジョニングプラットフォーム

-

トランスポートプラットフォーム、高密度波長分割多重(DWDM)

このドキュメントのタイミング情報は、2つのプロビジョニングプラットフォームに適用されます。トランスポートプラットフォームはタイミングを通じて使用します。throughタイミングでは、受信した「east」信号が送信した「west」信号を乗算し、受信した「west」信号が送信した「east」信号を乗算します。

タイミングアーキテクチャ

Timing, Communications and Control(TCC)カードとクロスコネクト(XC)カードは、SONET/SDH機器の業界標準に基づいてONS 15454のタイミング機能を制御します。冗長TCCカードとXCカードを使用して、耐障害性のある一般的なシステムハードウェアを提供します。

注:このドキュメントでは、TCCを一般的に使用してTCCカードのすべてのバリエーションを参照し、XCを一般的にすべてのバリエーションのXCカードを参照します。

ANSIシャーシには、2つのBuilding Integrated Timing Supply(BITS)Inポートが含まれています。両方のポートがAuxiliary Interface Protection(AIP)で終端します。 AIPの終端により、アクティブとスタンバイの両方のTCCカードでBITSを監視でき、電力サージによってバックプレーンが破損した場合でもBITSの適切な終端が保証されます。ETSIプラットフォームの場合、BITSインターフェイスはFront Mount Electrical Connection(FMEC)パネルにあります。

すべての同期インターフェイス(光ポート)は、TCCカードが管理するシステムタイミング基準から送信タイミングを取得します。XCカードは、各ポートに送信タイミングを提供します。TCCは次の同期機能を実行します。

-

監視、認定、参照の選択

-

アクティブな参照をフィルタしてロックするには

-

システムクロックの分配を管理する。

-

2つのBITS入力を終端する。

-

2つのBITS出力を生成する。

-

同期ステータスメッセージング(SSM)を処理および生成する。

-

メンテナンスの参照を切り替える。

-

同期アラームレポートを生成する。

タイミング分布

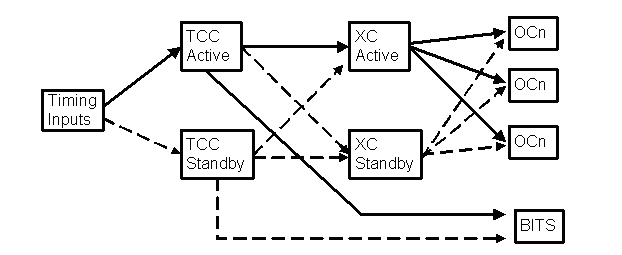

図1は、ANSIシステム内でのタイミングの分散方法を示しています。SDHバージョンは類似していますが、用語の変更は少しです。このセクションでは、例としてANSIバージョンを使用します。

注:実線はアクティブタイミング分布を表し、破線はスタンバイタイミング分布を表します。

図1 - ONS 15454 ANSIのタイミング選択と分布

各システムは、タイミングプロビジョニングに基づいて、複数の形式の入力または基準クロックを取ることができます。使用可能なタイミング入力は、BITS 1と2、光回線、および内部発振器です。これらの入力はすべて、アクティブなTCCカードからのタイミングだけが使用されますが、両方のTCCカードに供給されます。Provisioningを使用すると、基準クロックとして最大3つの入力を指定できます。各TCCカード内のタイミング回路は、独立して3つのリファレンスの中から1つのアクティブなリファレンスを選択し、そのリファレンスにロックします。生成されたクロックは、システムクロックまたはNEクロックと呼ばれます。

注:両TCCカードは互いにロックされません。

各TCCカードからのシステムクロックは両方のXCカードに分散され、すべてのOCnカードにクロックが供給されます。アクティブなXCカードからのクロックが選択されます。

注:SDHプラットフォームでは、タイミングはTCCカードから内部バスを介してラインカードに直接配信されます。

他のクロックを駆動するために、TCCカードは回線からBITSクロックを生成することもできます。

注:BITSタイミングループを防止するために、BITSアウトクロックをBITSインクロックから直接導出することはできません。

タイミング回路

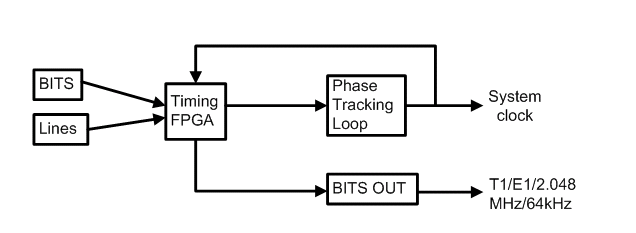

TCCカードのタイミング回路は、すべてのタイミング関連機能を処理します。図2には、高レベルのフローを示します。整合性を判断するために、Timing Field Programmable Gate Array(FPGA)はタイミング入力を処理します。システムクロックは、比較の基準として使用されます。選択したアクティブな参照がフェーズトラッキングループに送られ、システムクロック(NEクロック)が生成されます。回線から外部デバイスにタイミングを提供する信号に対してBITS信号を生成することもできます(BITSアウト)。BITS出力ポートは、さまざまな信号をサポートする2つの金属インターフェイスを提供します。

図2 - TCCのタイミング回路

リファレンスの認定と失敗

アクティブな参照の選択に影響を与える方法は2つあります。

-

プロビジョニング

-

参照認定

選択プロセスの候補となるのは、プロビジョニングされた基準クロックだけです。例外の1つは内部クロックです。これは、他のすべての参照が失敗した場合に常にデフォルトのクロックになります。ただし、プロビジョニングされた参照が必ずしもアクティブな参照として選択されるわけではありません。選択した参照はすべて、認定プロセスに合格する必要があります。

各参照は、状態変更に対して5ミリ秒ごとにポーリングされます。30秒間にわたって、TCCは各基準の周波数とワンダを計算します。周波数オフセットが±12.9 ppm以内の場合、基準は(受け入れ用に)修飾されます。周波数が有効な周波数境界(± 15 ppm、アクティブなBITSでは±16 ppm、非アクティブな参照では±13.1 ppm)を超えている場合、基準は不良(拒否)としてマークされ、ワンダがしきい値(2 ppm)を超えています。アラームを受信した場合、または信号がない場合、参照も不良とマークされます。アラームには、Loss of Signal(LOS;信号消失)、Loss of Frame(LOF;フレーム同期損失)、またはAlarm Indication Signal(AIS;アラーム表示信号)があります。 アクティブな参照が失敗すると、次の最適な参照の選択と切り替えが求められます。

回線同期基準を提供するためにプロビジョニングされたIOカードは、その受信信号を常にモニタします。ポートがLOS、LOF、またはAIS状態の場合、カードはTCCへの参照をオフにします。その結果、TCCはポートからの参照をbadとして宣言します。この参照が現在アクティブな参照である場合、次に最適な参照がアクティブな参照になります。

着信クロックにSSMが関連付けられている場合、SSMが参照選択に使用されます。SSMが使用されているかどうかにかかわらず、最高品質のクロックが常にアクティブクロックとして選択されます。同じ品質の参照が複数ある場合は、(プロビジョニングに基づいて)優先度が最も高い参照がアクティブ参照として選択されます。

要約すると、次の条件のいずれかが当てはまる場合、参照は受け入れられません。

-

光またはBITS入力がLOS、LOF、またはAISアラームを受信するか、インターフェイスがアウトオブサービスです。

-

SSMがDo-Not-Use(DUS)状態であるか、SSMはクロックの品質が低いことを示します(つまり、基準のSSM品質はTCCの品質よりも悪くなります)。

-

入力周波数は、BITSでは±15ppmを超え、30秒間(範囲外)の回線では±16ppmを超えます。

-

入力クロックが不安定である(つまり、クロックが2ppmを超えて移動する)。

-

30秒以上は認定されません。

フェーズロックループ

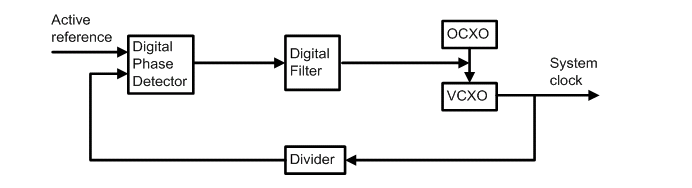

TCCのタイミング回路の中心には、フェーズロックループ(PLL)によって生成されたクロックジェネレータブロックがあります。 図3は、TCC上のシンプルなPLLを表しています。

図3 – フェーズロックループ

位相検出器は、アクティブな基準クロックとシステムクロックを比較します(すでに分周器で分割されています)。 位相オフセットがある場合は、オフセットに比例した電圧レベルが生成されます。オフセットがない場合、出力は生成されません。フィルタは、ある期間の電圧信号を平滑化または平均化し、その平均値を電圧制御水晶発振器(VCXO)に供給します。 電圧は、VCXOの位相と周波数を調整します。VCXOの出力は、システムクロック(またはNEクロック)です。 出力の一部がループにフィードバックされ、プロセスが繰り返されます。システムクロックがアクティブな基準を追跡すると、クロックがロックされ、TCCが通常クロックモードに入ります。

VCXOは、Oven Controlled Crystal Oscillator(OCXO)とフィルタリングされた基準クロックの間の小さなPLLによってさらに安定化される。

注:図を簡略化するために、この小さなPLLは示されていません。

その結果、システムクロックの安定性が向上します。TCCで使用されるOCXOは、ホールドオーバーの安定性とフリーランの精度を表すストラタム3で評価されることに注意してください。

カードレベル同期のサポート

光カード

-

システムクロックは、すべてのSONET送信インターフェイスに対して時間を掛けます。

-

入力タイミングと出力タイミングの違いを解決するには、ポインタ調整を使用します。

DS1/DS3カード

-

元のDSx入力レートによって、出力のデータレートが決まります。データレートは、スルータイミングモードのNEクロックとは完全に独立しています。

-

SONETネットワークの初期マッピングおよびポインタ調整でスタッフビットを使用して、NEレートとデータレートの違いを解決します。

DS3XMカード

-

出力ラインレートはNEクロックにロックされます。

-

DS3内の個々のDS1は、入力周波数を維持します。

タイミングモード

ONS 15454は次のタイミングモードをサポートしています。

-

外部

-

LINE

-

混合

TCCカードには、ホールドオーバーとフリーランニングタイミングのサポートを提供するために使用できる内部ストラタム3クロックがあります。

注:スルータイミングとポートごとのループタイミングは、追加のタイミングモードです。ただし、ONS 15454プロビジョニングプラットフォームでは、これらのモードはサポートされていません。

注:電気非同期インターフェイスはthrough-timedであり、システムタイミングを参照しません。これらの非同期ポートでは、送信タイミングはその非同期信号の受信タイミングから導出されます。

外部タイミング

このモードは、BITSやタイミングDS-1/E1などの外部タイミングデバイスからタイミングを取得します。外部タイミングデバイスの品質レベルは、内部ストラタム3クロックよりも優れています。

回線タイミング

回線タイミングは、1つ以上の光インターフェイスからタイミング基準を導出します。複数の光インターフェイスを備えた光カードでは、1つのインターフェイスのみをタイミング基準ポートとしてプロビジョニングできます。着信リカバリクロックは19.44MHz信号に変換され、TCCカードに送信され、タイミング基準として認定されます。回線タイミングモードでは、使用可能なタイミング基準は光インターフェイスと内部クロックです。

注:光ポートが1+1としてプロビジョニングされている場合、タイミングリファレンスとしてプロビジョニングされるのは動作中のポートだけです。保護ポートは、スイッチオーバー中に自動的に選択されます。

混合タイミング

混合モードタイミングでは、内部クロックだけでなく、外部(BITS1/BITS2)と回線(光インターフェイス)の両方のタイミング基準を選択できます。混合モードタイミングを使用する場合は注意してください。これは、タイミングループが発生しやすいためです。したがって、混合モードタイミングを使用する前に、慎重に計画してください。または、ループドBITSを使用します。

クロックモード

通常モード

通常動作モードでは、TCCは外部タイミングソースにロックされます。

ファストスタートモード

発振器は、発振器の周波数から遠い基準クロックの高速「プルイン」にFast-startモードを使用します。ファストスタートは「取得状態」と呼ばれることもあります。TCCがTCCカードがすでに実行されているレートに近い基準に変更されると、モードは直接Normalに変更されます。

ホールドオーバーモード

ホールドオーバーモードでは、外部または回線のタイミング基準がすべて失われ、クロックは通常の動作モードで参照されるタイミングデータを使用して出力信号を制御します。ただし、ホールドオーバー周波数は、タイミング基準が使用可能になるまで時間の経過とともに変動します。以前のタイミング基準が失われる140秒未満で使用可能であった場合、タイミング基準が失われると、TCCはフリーランニングモードに入ります。

このモードは、最後に修飾されたタイミング基準からの平均140秒のデータを使用して内部クロックを増強するため、フリーランニングモードよりも優れています。TCCは、リファレンスが切り替え可能になるか、ドリフトが範囲外になるまで、このモードのままになります。最初の24時間は、ホールドオーバーモードへの移行によってトラフィックが中断されないことが保証されます。

フリーランニングモード

フリーランニングモードは、TCCカードの内部クロックのみを参照します。このモードは、参照として特別にプロビジョニングされていない場合でも、他の参照が失われた場合のデフォルトモードでもあります。ネットワークがTCCカードの内部クロックを唯一またはプライマリタイミングソースとして使用していないことを確認します。

同期を計画するためのガイドライン

タイミング設計の特長

適切なタイミング設計:

-

論理タイミング階層を組み込みます。

-

効率的な同期を提供

-

タイミングループを回避します。

-

タイミング障害から迅速に回復。

少数のノードよりも大きいネットワークに対して、冗長で正確な外部タイミングソースを常に使用するのが最適です。実際のネットワークでは、これは常に可能であるとは限らず、必要であるとは限りません。

内部タイミングは、通常動作時のプライマリタイミングソースとして使用することを意図していません。シスコでは、他のすべてのタイミングソースに障害が発生した場合に使用可能な内部クロックを使用して、プライマリネットワークタイミングに高品質のソース(Primary Reference Source/Primary Reference Clock(PRS/PRC)クロックを使用することを推奨します。

トレーサビリティを高めるために、マスターノードからデイジーチェーン方式でタイミング設定されるONS 15454ノードの数を最小限に抑えます。一般的なガイドラインとして、プライマリ方向には最大7つのノード、セカンダリ方向には最大13のノードを設定できます。タイミングループを回避するために、リング内の回線タイミングを慎重に計画します。

ノードが自身のクロックを追跡しようとすると、タイミングループにより大きな周波数エラーが発生する可能性があります。その結果、ONS 15454ノードが繰り返しホールドオーバー、ファーストスタート、またはフリーランタイミングモードに入ります。多くの場合、タイミングループが存在することを示すアラームはありません。

関連情報

更新履歴

| 改定 | 発行日 | コメント |

|---|---|---|

1.0 |

01-Jan-2006

|

初版 |

フィードバック

フィードバック