Cronometragem e sincronização no Cisco ONS 15454

Contents

Introduction

Este documento fornece diretrizes para planejar a temporização e a sincronização no Cisco ONS 15454.

Prerequisites

Requirements

A Cisco recomenda que você tenha conhecimento destes tópicos:

-

Cisco ONS 15454

Componentes Utilizados

As informações neste documento são baseadas nestas versões de software e hardware:

-

Cisco ONS 15454

The information in this document was created from the devices in a specific lab environment. All of the devices used in this document started with a cleared (default) configuration. If your network is live, make sure that you understand the potential impact of any command.

Conventions

Consulte as Convenções de Dicas Técnicas da Cisco para obter mais informações sobre convenções de documentos.

Informações de Apoio

O produto contém:

-

A plataforma de provisionamento do American National Standards Institute/Synchronous Optical NETwork (ANSI/SONET)

-

A plataforma de provisionamento ETSI/ITU/SDH (European Telecommunications Standards Institute/International Telecommunications Union/Synchronous Digital Hierarchy)

-

A plataforma de transporte, DWDM (Dense Wavelength Division Multiplexing, multiplexação de divisão de comprimento de onda denso)

As informações de temporização neste documento se aplicam às duas plataformas de provisionamento. A plataforma de transporte usa o tempo. Através da temporização, o sinal recebido "Este" multiplicou o sinal transmitido "Oeste" e o sinal recebido "Oeste" multiplicou o sinal transmitido "Este".

Arquitetura de cronometragem

As placas Timing, Communications and Control (TCC) e Cross Connect (XC) controlam a função de temporização no ONS 15454 com base nos padrões do setor para equipamentos SONET/SDH. Use placas TCC e XC redundantes para fornecer hardware de sistema comum tolerante a falhas.

Observação: este documento usa TCC genericamente para se referir a todas as variações da placa TCC e XC genericamente para se referir a todas as variações da placa XC.

O chassi ANSI contém duas BITS (Building Integrated Timing Supply, Fonte de tempo integrada do edifício) em portas. Ambas as portas terminam na Proteção de Interface Auxiliar (AIP - Auxiliary Interface Protection). A terminação no AIP permite que as placas TCC ativas e em standby monitorem o BITS e garante a terminação correta do BITS, mesmo que o backplane esteja danificado devido a um surto de energia. Para a plataforma ETSI, as interfaces BITS estão localizadas no painel Conexão elétrica de montagem frontal (FMEC).

Todas as interfaces síncronas (portas ópticas) derivam o tempo de transmissão da referência de temporização do sistema que a placa TCC gerencia. As placas XC fornecem temporização de transmissão para cada porta. O TCC executa estas funções de sincronização:

-

Para monitorar, qualificar e selecionar referência.

-

Para filtrar e bloquear na referência ativa.

-

Para gerenciar a distribuição do relógio do sistema.

-

Para terminar duas entradas de BITS.

-

Para gerar duas saídas de BITS.

-

Para processar e gerar mensagens de status de sincronização (SSM).

-

Para mudar de referência para manutenção.

-

Para gerar relatórios de alarme de sincronização.

Distribuição de tempo

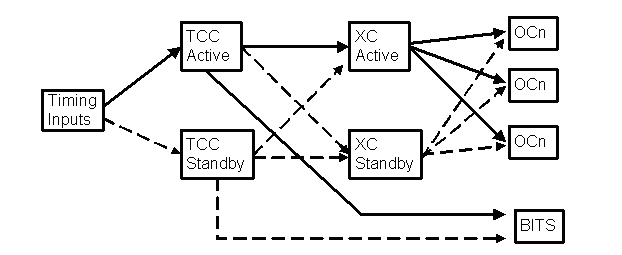

A Figura 1 indica como a temporização é distribuída dentro de um sistema ANSI. A versão SDH é semelhante, mas com pequenas alterações na terminologia. Esta seção usa a versão ANSI como exemplo.

Observação: as linhas sólidas representam a distribuição de tempo ativa e as linhas tracejadas representam a distribuição de tempo em espera.

Figura 1: Seleção de cronometragem e distribuição no ONS 15454 ANSI

Cada sistema pode tomar várias formas de entradas ou relógios de referência, com base no provisionamento de tempo. As entradas de temporização disponíveis são BITS 1 e 2, linhas ópticas e o oscilador interno. Todas essas entradas são alimentadas para ambas as placas TCC, embora somente a temporização da placa TCC ativa seja usada. Você pode usar o provisionamento para designar até três entradas como relógios de referência. O circuito de temporização dentro de cada placa TCC qualifica e seleciona de forma independente uma referência ativa entre as três referências e bloqueia essa referência. O relógio resultante é chamado relógio do sistema ou relógio NE.

Observação: ambas as placas TCC não se prendem umas às outras.

O relógio do sistema de cada placa TCC é distribuído para ambas as placas XC, que alimentam o relógio em todas as placas OCn. O relógio da placa XC ativa está selecionado.

Observação: nas plataformas SDH, a temporização é distribuída das placas TCC diretamente às placas de linha em um barramento interno.

Para acionar outros relógios, as placas TCC também podem gerar relógios BITS das linhas.

Observação: os relógios BITS Out não podem ser derivados diretamente dos relógios BITS In para evitar loops de temporização BITS.

Circuito de cronometragem

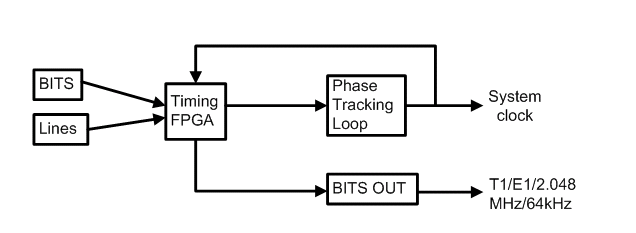

O circuito de temporização em placas TCC lida com todas as funções relacionadas à temporização. A Figura 2 mostra um fluxo de alto nível. Para determinar a integridade, o FPGA (Timing Field Programmable Gate Array) processa as entradas de temporização. O relógio do sistema é usado como referência para a comparação. A referência ativa selecionada é alimentada no Loop de Rastreamento de Fase, que produz o relógio do sistema (relógio NE). Os sinais de BITS também podem ser gerados para sinais que vêm das linhas para fornecer temporização para dispositivos externos (saída de BITS). As portas de saída BITS fornecem duas interfaces metálicas que suportam uma variedade de sinais.

Figura 2: Circuito de cronometragem em TCC

Qualificação e falha de referência

Há duas maneiras de influenciar a seleção da referência ativa:

-

Aprovisionamento

-

Qualificação de referência

Somente os relógios de referência provisionados são candidatos ao processo de seleção. Uma exceção é o relógio interno, que é sempre o relógio padrão quando todas as outras referências falham. No entanto, uma referência provisionada não é necessariamente selecionada como referência ativa. Qualquer referência selecionada deve passar no processo de qualificação.

Cada referência é pesquisada a cada cinco milissegundos para alterações de estado. Durante um período de 30 segundos, o TCC computa a frequência e vagarosamente para cada referência. Qualifica-se uma referência (para aceitação) quando a diferença de frequência estiver entre ± 12,9 ppm. Uma referência é marcada como ruim (rejeitada) quando a frequência estiver fora dos limites de frequência válidos (± 15 ppm para BITS ativo, ± 16 ppm para linhas ativas e ± 13,1 ppm para referências não ativas) e quando o vento estiver além do limiar (2 ppm). Uma referência também é marcada como ruim quando um alarme é recebido ou se não há sinal. O alarme pode ser Perda de Sinal (LOS), Perda de Quadro (LOF) ou Sinal de Indicação de Alarme (AIS). A falha da referência ativa solicita a seleção e a comutação para a próxima melhor referência.

Uma placa de E/S provisionada para fornecer referência de sincronização de linha monitora constantemente seu sinal recebido. Se a porta estiver em um estado LOS, LOF ou AIS, a placa desliga a referência ao TCC. Como resultado, a TCC declara a referência da porta como ruim. Se essa referência for a referência ativa atual, a próxima melhor referência se tornará a referência ativa.

Se um relógio de entrada tiver SSM associado a ele, o SSM será usado para a seleção de referência. O relógio de mais alta qualidade, seja ou não SSM usado, é sempre selecionado como o relógio ativo. Quando há mais de uma referência que tem a mesma qualidade, a que tem a prioridade mais alta (com base no provisionamento) é selecionada como referência ativa.

Em resumo, não é aceite uma referência se qualquer destas condições for verdadeira:

-

A entrada óptica ou BITS recebe um alarme LOS, LOF ou AIS ou a interface está fora de serviço.

-

O SSM está no estado do não uso (DUS), ou o SSM indica que o relógio é de menor qualidade (em outras palavras, a qualidade do SSM da referência é pior que a do TCC).

-

A frequência de entrada é inferior em mais de ± 15 ppm para BITS ou ± 16 ppm para linhas durante um período de 30 segundos (fora dos limites).

-

O relógio de entrada é instável (o que significa que o relógio oscila a mais de 2 ppm).

-

Não está qualificado por pelo menos 30 segundos.

Loop de Fase Bloqueado

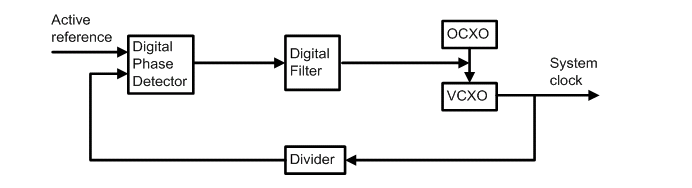

No coração do circuito de temporização em TCC está o bloco gerador de clock gerado pelo loop de fase bloqueada (PLL). A Figura 3 representa uma PLL simplificada em TCC.

Figura 3: Loop bloqueado em fase

O detector de fase compara o relógio de referência ativo com o relógio do sistema (já dividido através do divisor). Se houver um deslocamento de fase, um nível de voltagem proporcional ao deslocamento é gerado. Se não houver deslocamento, nenhuma saída será gerada. O filtro suaviza ou faz a média do sinal de voltagem durante algum período e alimenta a média no Voltage Controlled Crystal Oscillator (VCXO). A voltagem ajusta a fase e a frequência do VCXO. A saída de VCXO é relógio do sistema (ou relógio NE). Parte da saída é alimentada de volta no loop para repetir o processo. Quando o relógio do sistema rastreia a referência ativa, o relógio é bloqueado e o TCC entra no modo de relógio normal.

O VCXO é ainda estabilizado por uma PLL menor entre o Oscilador de Cristal Comprovado (OCXO - Oven Controled Crystal Oscillator) e o relógio de referência filtrado.

Observação: para simplificar o diagrama, essa PLL menor não é mostrada aqui.

O resultado é que o relógio do sistema é mais estável. Observe que o OCXO usado na TCC é classificado no Stratum 3 por sua estabilidade remanescente e precisão livre.

Suporte para sincronização no nível da placa

Placas ópticas

-

O relógio do sistema aumenta o tempo de todas as interfaces de transmissão SONET.

-

Use ajustes de ponteiro para resolver diferenças entre temporização de entrada e saída.

Placas DS1/DS3

-

A taxa de entrada DSx original determina a taxa de dados da saída. A taxa de dados é completamente independente do relógio NE para o modo de cronometragem por passagem.

-

Use bits de material no mapeamento inicial e ajustes de ponteiro na rede SONET para resolver diferenças entre a taxa NE e a taxa de dados.

Placas DS3XM

-

A taxa de linha de saída está bloqueada para o relógio NE.

-

Os DS1s individuais dentro do DS3 mantêm sua frequência de entrada.

Modos de cronometragem

O ONS 15454 suporta estes modos de temporização:

-

Externos

-

Linha

-

Misto

As placas TCC têm um relógio Stratum 3 interno disponível para fornecer suporte de Holdover e cronometragem de execução livre.

Observação: através da temporização e da temporização do loop por porta, há modos de temporização adicionais. No entanto, as plataformas de provisionamento ONS 15454 não suportam esses modos.

Observação: as interfaces assíncronas elétricas são cronometradas por meio de tempo e não fazem referência à temporização do sistema. Para essas portas assíncronas, o tempo de transmissão é derivado do tempo recebido para esse sinal assíncrono.

Temporização externa

Esse modo deriva temporização de um dispositivo de temporização externo, por exemplo, BITS ou DS-1/E1 de temporização. O nível de qualidade do dispositivo externo de temporização é melhor do que o relógio interno Stratum 3.

Temporização da linha

A temporização da linha deriva a referência de temporização de uma ou mais interfaces ópticas. As placas ópticas com várias interfaces ópticas podem provisionar apenas uma interface como uma porta de referência de temporização. O relógio recuperado recebido é convertido em um sinal de 19,44 MHz, transmitido às placas TCC e qualificado como referência de temporização. No modo de temporização de linha, as referências de temporização disponíveis são interfaces ópticas e o relógio interno.

Observação: quando as portas ópticas são provisionadas como 1+1, somente a porta em funcionamento é provisionada como uma referência de temporização. A porta de proteção é selecionada automaticamente durante um comutador.

Temporização mista

A temporização do modo misto permite que as referências de temporização tanto de Externo (BITS1/BITS2) como de Linha (interfaces ópticas) sejam selecionadas, bem como do relógio interno. Tenha cuidado ao usar a temporização do modo misto, pois os loops de temporização podem ocorrer facilmente. Portanto, planeje cuidadosamente antes de usar a temporização do modo misto. Como alternativa, use BITS em loop.

Modos de Relógio

Modo normal

No modo de operação Normal, o TCC está bloqueado em uma fonte de temporização externa.

Modo de início rápido

Um oscilador usa o modo de início rápido para "pull-in" rápido de um relógio de referência cuja frequência é muito diferente da do oscilador. O início rápido é às vezes chamado de "Estado de aquisição". Se o TCC mudar para uma referência próxima à taxa na qual a placa TCC já está em execução, o modo muda diretamente para Normal.

Modo holdover

No modo Holdover, todas as referências de temporização externa ou de linha são perdidas e o relógio usa dados de temporização referenciados no modo operacional normal para controlar seu sinal de saída. No entanto, a frequência de holdover deriva com o tempo até que uma referência de tempo fique disponível. Se a referência de temporização anterior estava disponível por menos de 140 segundos antes de ser perdida, a TCC entra no modo de execução livre quando a referência de temporização é perdida.

Esse modo é melhor que o modo de execução livre porque usa a média de 140 segundos de dados da última referência de temporização qualificada para aumentar seu relógio interno. O TCC permanece nesse modo até que uma referência se torne disponível para o switch ou o desvio esteja fora dos limites. É garantido que o tráfego não seja interrompido por uma transição para o modo de transferência durante as primeiras 24 horas.

Modo de execução livre

O modo de execução livre refere-se apenas ao relógio interno na placa TCC. Esse modo também é o modo padrão quando outras referências são perdidas, mesmo quando não é especificamente provisionado como referência. Certifique-se de que sua rede não opere com o relógio interno da placa TCC como a única ou principal fonte de temporização.

Diretrizes para planejar a sincronização

Recursos do design de bom tempo

Bom design de cronometragem:

-

Incorpora uma hierarquia de temporização lógica.

-

Fornece sincronização eficiente.

-

Evita loops de temporização.

-

Recupera-se rapidamente de falhas de temporização.

É sempre melhor ter fontes de temporização externa redundantes e precisas para uma rede maior que alguns nós. Em redes reais, isso nem sempre é possível ou necessário.

A temporização interna não deve ser usada como fonte de temporização primária durante a operação normal. A Cisco recomenda que você use uma fonte de qualidade superior (preferencialmente relógios de fonte de referência primária/relógio de referência principal (PRS/PRC) para temporização de rede primária com o relógio interno disponível para horários em que todas as outras fontes de temporização falham.

Para alta rastreabilidade, minimize o número de nós ONS 15454 cronometrados de linha em cadeia de margarida de um nó mestre. Como diretriz geral, você pode ter até sete nós para a direção primária e 13 nós para a direção secundária. Planeje cuidadosamente a temporização da linha em um anel para evitar loops de temporização.

Os loops de temporização podem causar erros de grande frequência à medida que o nó tenta controlar seu próprio relógio, o que, por sua vez, pode resultar em nós ONS 15454 para entrar repetidamente nos modos Holdover, Fast-start ou Free-run timing . Frequentemente, não há alarme para indicar que existe um loop de temporização.

Informações Relacionadas

Histórico de revisões

| Revisão | Data de publicação | Comentários |

|---|---|---|

1.0 |

01-Jan-2006

|

Versão inicial |

Feedback

Feedback