Sincronización y sincronización en Cisco ONS 15454

Contenido

Introducción

Este documento proporciona pautas para planificar el tiempo y la sincronización en Cisco ONS 15454.

Prerequisites

Requirements

Cisco recomienda que tenga conocimiento sobre estos temas:

-

Cisco ONS 15454

Componentes Utilizados

La información que contiene este documento se basa en las siguientes versiones de software y hardware.

-

Cisco ONS 15454

The information in this document was created from the devices in a specific lab environment. All of the devices used in this document started with a cleared (default) configuration. If your network is live, make sure that you understand the potential impact of any command.

Convenciones

Antecedentes

El producto contiene:

-

La plataforma de aprovisionamiento del American National Standards Institute/Synchronous Optical NET (ANSI/SONET)

-

La plataforma de aprovisionamiento del Instituto Europeo de Estándares de Telecomunicaciones/Unión Internacional de Telecomunicaciones/Jerarquía digital síncrona (ETSI/ITU/SDH)

-

La plataforma de transporte, DWDM (DWDM)

La información de temporización de este documento se aplica a las dos plataformas de aprovisionamiento. La plataforma de transporte se utiliza a través del tiempo. A través de la temporización, la señal "este" recibida envía la señal "oeste" transmitida y la señal "oeste" recibida hace que la señal "este" transmitida se transforme.

Arquitectura de sincronización

Las tarjetas Timing, Communications and Control (TCC) y las tarjetas de conexión cruzada (XC) controlan la función de temporización en el ONS 15454 según los estándares del sector para equipos SONET/SDH. Utilice tarjetas TCC y XC redundantes para proporcionar hardware de sistema común tolerante a fallos.

Nota: Este documento utiliza TCC de forma genérica para referirse a todas las variaciones de la tarjeta TCC y XC de forma genérica para referirse a todas las variaciones de la tarjeta XC.

El chasis ANSI contiene dos fuentes de sincronización integradas de edificios (BITS) en puertos. Ambos puertos terminan en la protección de interfaz auxiliar (AIP). La terminación en el AIP permite que las tarjetas TCC activas y en espera monitoreen el BITS, y asegura la terminación adecuada del BITS incluso si la placa de interconexiones está dañada debido a una sobrecarga de energía. Para la plataforma ETSI, las interfaces BITS se encuentran en el panel Conexión eléctrica de montaje frontal (FMEC).

Todas las interfaces síncronas (puertos ópticos) derivan la sincronización de transmisión de la referencia de sincronización del sistema que administra la tarjeta TCC. Las tarjetas XC proporcionan temporización de transmisión a cada puerto. TCC realiza estas funciones de sincronización:

-

Para supervisar, calificar y seleccionar referencia.

-

Para filtrar y bloquear la referencia activa.

-

Para gestionar la distribución del reloj del sistema.

-

Para terminar dos entradas BITS.

-

Para generar dos salidas BITS.

-

Para procesar y generar mensajes de estado de sincronización (SSM).

-

Para cambiar la referencia para el mantenimiento.

-

Para generar informes de alarma de sincronización.

Distribución de sincronización

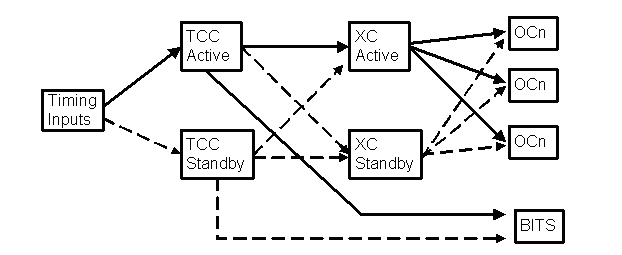

La figura 1 indica cómo se distribuye el tiempo dentro de un sistema ANSI. La versión de SDH es similar, pero con cambios de terminología menores. Esta sección utiliza la versión ANSI como ejemplo.

Nota: Las líneas sólidas representan la distribución de temporización activa y las líneas discontinuas representan la distribución de temporización en espera.

Figura 1: Selección y distribución de temporización en ONS 15454 ANSI

Cada sistema puede adoptar varias formas de entradas o relojes de referencia, en función del aprovisionamiento de temporización. Las entradas de temporización disponibles son BITS 1 y 2, líneas ópticas y el oscilador interno. Todas estas entradas se envían a ambas tarjetas TCC, aunque sólo se utiliza la sincronización de la tarjeta TCC activa. Puede utilizar el aprovisionamiento para designar hasta tres entradas como relojes de referencia. El circuito de temporización dentro de cada tarjeta TCC califica y selecciona de forma independiente una referencia activa entre las tres referencias y se bloquea en esa referencia. El reloj resultante se denomina reloj del sistema o reloj NE.

Nota: Ambas tarjetas TCC no se bloquean entre sí.

El reloj del sistema de cada tarjeta TCC se distribuye a ambas tarjetas XC, que alimentan el reloj en todas las tarjetas OCn. Se selecciona el reloj de la tarjeta XC activa.

Nota: En las plataformas SDH, la temporización se distribuye desde las tarjetas TCC directamente a las tarjetas de línea a través de un bus interno.

Para impulsar otros relojes, las tarjetas TCC también pueden generar relojes BITS a partir de las líneas.

Nota: Los relojes BITS Out no se pueden derivar directamente de BITS In clocks para evitar los loops de temporización BITS.

Circulación de sincronización

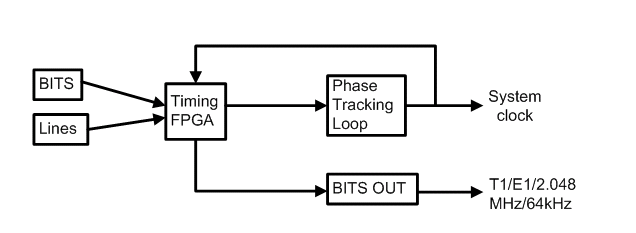

El circuito de temporización en las tarjetas TCC maneja todas las funciones relacionadas con la temporización. La figura 2 muestra un flujo de alto nivel. Para determinar la integridad, Timing Field Programmable Gate Array (FPGA) procesa las entradas de temporización. El reloj del sistema se utiliza como referencia para la comparación. La referencia activa seleccionada se introduce en el bucle de seguimiento de fase, que produce el reloj del sistema (reloj NE). Las señales BITS también se pueden generar para las señales que provienen de las líneas para proporcionar temporización a los dispositivos externos (BITS Out). Los puertos BITS Out proporcionan dos interfaces metálicas que admiten una variedad de señales.

Figura 2: Circunstancia de sincronización en TCC

Calificación y fallo de referencia

Hay dos formas de influir en la selección de la referencia activa:

-

Aprovisionamiento

-

Calificación de referencia

Sólo los relojes de referencia aprovisionados son candidatos para el proceso de selección. Una excepción es el reloj interno, que siempre es el reloj predeterminado cuando fallan todas las demás referencias. Sin embargo, una referencia aprovisionada no se selecciona necesariamente como referencia activa. Cualquier referencia seleccionada debe pasar el proceso de calificación.

Cada referencia se sondea cada cinco milisegundos para los cambios de estado. Durante un período de 30 segundos, el TCC calcula la frecuencia y la fluctuación para cada referencia. Se califica una referencia (para su aceptación) cuando el desplazamiento de la frecuencia se encuentra dentro de ± 12,9 ppm. Una referencia se marca como mala (rechazada) cuando la frecuencia se encuentra fuera de los límites de frecuencia válidos (± 15 ppm para los BITS activos, ± 16 ppm para las líneas activas y ± 13,1 ppm para las referencias no activas) y la fluctuación está por encima del umbral (2 ppm). Una referencia también se marca mal cuando se recibe una alarma o si no hay señal. La alarma puede ser Pérdida de señal (LOS), Pérdida de trama (LOF) o Señal de indicación de alarma (AIS). El fallo de la referencia activa solicita la selección y el cambio a la siguiente mejor referencia.

Una tarjeta IO aprovisionada para proporcionar referencia de sincronización de línea monitorea constantemente su señal recibida. Si el puerto está en estado LOS, LOF o AIS, la tarjeta desactiva la referencia a TCC. Como resultado, el TCC declara la referencia del puerto como mala. Si esta referencia es la referencia activa actual, la siguiente mejor referencia se convierte en la referencia activa.

Si un reloj entrante tiene SSM asociado, SSM se utiliza para la selección de referencia. El reloj de mayor calidad, se utilice o no SSM, siempre se selecciona como el reloj activo. Cuando hay más de una referencia que tiene la misma calidad, la que tiene la prioridad más alta (basada en el aprovisionamiento) se selecciona como referencia activa.

En resumen, no se acepta una referencia si se cumple alguna de estas condiciones:

-

La entrada óptica o BITS recibe una alarma LOS, LOF o AIS, o la interfaz está fuera de servicio.

-

El SSM se encuentra en el estado No-usar (DUS) o el SSM indica que el reloj es de menor calidad (en otras palabras, la calidad SSM de la referencia es peor que la de TCC).

-

La frecuencia de entrada se reduce en más de ± 15 ppm para BITS o ± 16 ppm para líneas durante un período de 30 segundos (fuera de límites).

-

El reloj de entrada es inestable (lo que significa que el reloj desciende a más de 2 ppm).

-

No está calificado durante al menos 30 segundos.

Fase Bloqueada Loop

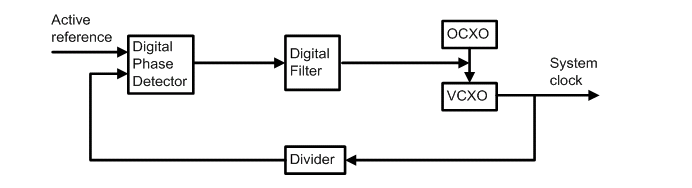

En el corazón del circuito de temporización del TCC se encuentra el bloque del generador de reloj generado por el loop de fase bloqueada (PLL). La figura 3 representa una PLL simplificada en TCC.

Figura 3 - Fase Bloqueada Loop

El detector de fases compara el reloj de referencia activo con el reloj del sistema (ya dividido a través del divisor). Si hay un desplazamiento de fase, se genera un nivel de voltaje proporcional al desplazamiento. Si no hay desplazamiento, no se genera ninguna salida. El filtro suaviza o promedia la señal de voltaje durante algún período y alimenta la media en el oscilador de cristal controlado por voltaje (VCXO). El voltaje ajusta la fase y la frecuencia de VCXO. La salida de VCXO es el reloj del sistema (o reloj NE). Parte del resultado se devuelve al loop para repetir el proceso. Cuando el reloj del sistema realiza un seguimiento de la referencia activa, el reloj se bloquea y TCC ingresa en el modo de reloj normal.

El VCXO se estabiliza aún más con una PLL más pequeña entre Oven Controlled Crystal Oscillator (OCXO) y el reloj de referencia filtrado.

Nota: Para simplificar el diagrama, esta PLL más pequeña no se muestra aquí.

El resultado es que el reloj del sistema es más estable. Observe que el OCXO utilizado en el TCC está clasificado en el Stratum 3 por su estabilidad de retención y exactitud de ejecución libre.

Soporte de Sincronización de Nivel de Tarjeta

Tarjetas ópticas

-

El reloj del sistema horaba todas las interfaces de transmisión SONET.

-

Utilice los ajustes del puntero para resolver las diferencias entre la temporización de entrada y salida.

Tarjetas DS1/DS3

-

La velocidad de entrada DSx original determina la velocidad de datos de la salida. La velocidad de datos es completamente independiente del reloj NE para el modo de temporización a través.

-

Utilice los bits de material en los ajustes iniciales de asignación y puntero en la red SONET para resolver las diferencias entre la velocidad NE y la velocidad de datos.

Tarjetas DS3XM

-

La velocidad de la línea de salida está bloqueada al reloj NE.

-

Los DS1 individuales dentro del DS3 conservan su frecuencia de entrada.

Modos de sincronización

ONS 15454 admite estos modos de sincronización:

-

Externo

-

Línea

-

Mixto

Las tarjetas TCC tienen un reloj interno Stratum 3 disponible para proporcionar soporte de Holdover y temporización de ejecución libre.

Nota: A través de la temporización y la temporización del loop por puerto son modos de temporización adicionales. Sin embargo, las plataformas de aprovisionamiento ONS 15454 no admiten estos modos.

Nota: Las interfaces asíncronas eléctricas se realizan a tiempo completo y no hacen referencia a la temporización del sistema. Para estos puertos asincrónicos, la temporización de transmisión se deriva de la sincronización recibida para esa señal asincrónica.

Temporización externa

Este modo deriva la temporización de un dispositivo de temporización externo, por ejemplo, BITS o la sincronización DS-1/E1. El nivel de calidad del dispositivo de temporización externo es mejor que el reloj interno de Estrato 3.

Temporización de línea

La temporización de línea deriva la referencia de temporización de una o más interfaces ópticas. Las tarjetas ópticas con varias interfaces ópticas sólo pueden aprovisionar una interfaz como puerto de referencia de sincronización. El reloj recuperado entrante se convierte en una señal de 19,44 MHz, se transmite a las tarjetas TCC y se califica como referencia de temporización. En el modo de temporización de línea, las referencias de temporización disponibles son interfaces ópticas y el reloj interno.

Nota: Cuando los puertos ópticos se aprovisionan como 1+1, sólo el puerto en funcionamiento se aprovisiona como referencia de temporización. El puerto de protección se selecciona automáticamente durante un switch.

Temporización mixta

La temporización del modo mixto permite seleccionar tanto las referencias de temporización Externas (BITS1/BITS2) como Línea (interfaces ópticas), así como el reloj interno. Tenga cuidado cuando utilice la temporización de modo mixto, porque los loops de sincronización pueden ocurrir fácilmente. Por lo tanto, planifique cuidadosamente antes de utilizar la temporización de modo mixto. Alternativamente, utilice BITS con loop.

Modos de reloj

Modo normal

En el modo de funcionamiento normal, TCC se bloquea en una fuente de sincronización externa.

Modo de inicio rápido

Un oscilador utiliza el modo de inicio rápido para la "incorporación" rápida de un reloj de referencia cuya frecuencia es muy distinta a la del oscilador. El inicio rápido se denomina a veces "Estado de adquisición". Si TCC cambia a una referencia cercana a la velocidad a la que la tarjeta TCC ya se ejecuta, el modo cambia directamente a Normal.

Modo de mantenimiento

En el modo Holdover, se pierden todas las referencias de temporización externas o de línea y el reloj utiliza los datos de temporización a los que se hace referencia mientras está en el modo de funcionamiento normal para controlar su señal de salida. Sin embargo, la frecuencia de retención se desplaza con el tiempo hasta que una referencia de temporización esté disponible. Si la referencia de temporización anterior estuvo disponible durante menos de 140 segundos antes de que se perdiera, TCC ingresa en el modo de ejecución libre cuando se pierde la referencia de temporización.

Este modo es mejor que el modo de ejecución libre porque utiliza el promedio de 140 segundos de datos de la última referencia de temporización calificada para aumentar su reloj interno. El TCC permanece en este modo hasta que una referencia esté disponible para conmutar o la deriva esté fuera de límites. Se garantiza que el tráfico permanezca ininterrumpido por una transición al modo de retención durante las primeras 24 horas.

Modo de ejecución libre

El modo de ejecución libre sólo hace referencia al reloj interno en la tarjeta TCC. Este modo también es el modo predeterminado cuando se pierden otras referencias, incluso cuando no se proporciona específicamente como referencia. Asegúrese de que su red no funcione con el reloj interno de la tarjeta TCC como fuente de sincronización única o principal.

Pautas para Planificar la Sincronización

Funciones de diseño de buen tiempo

Diseño de sincronización adecuado:

-

Incorpora una jerarquía de temporización lógica.

-

Proporciona una sincronización eficaz.

-

Evita los loops de sincronización.

-

Se recupera rápidamente de las fallas de sincronización.

Siempre es mejor tener fuentes de sincronización externas redundantes y precisas para una red mayor que unos pocos nodos. En las redes reales, esto no siempre es posible o necesario.

La temporización interna no está diseñada para utilizarse como fuente de sincronización principal durante el funcionamiento normal. Cisco recomienda utilizar un origen de mayor calidad (preferiblemente temporizadores de origen de referencia principal/reloj de referencia principal (PRS/PRC)) para la sincronización de la red principal con el reloj interno disponible para los momentos en que fallan todas las demás fuentes de sincronización.

Para una alta rastreabilidad, minimice el número de líneas de nodos ONS 15454 cronometradas en cadena de margarita desde un nodo maestro. Como directriz general, puede tener hasta siete nodos para la dirección primaria y 13 nodos para la dirección secundaria. Planifique cuidadosamente la temporización de línea en un anillo para evitar loops de temporización.

Los loops de temporización pueden causar errores de frecuencia grandes mientras el nodo intenta realizar un seguimiento de su propio reloj, lo que a su vez puede dar lugar a que los nodos ONS 15454 ingresen repetidamente modos de temporización de espera, inicio rápido o ejecución libre. A menudo no hay alarma para indicar que existe un loop de sincronización.

Información Relacionada

Historial de revisiones

| Revisión | Fecha de publicación | Comentarios |

|---|---|---|

1.0 |

01-Jan-2006

|

Versión inicial |

Comentarios

Comentarios