Árvore de falha de erro de paridade de Cisco 7200

Contents

Introduction

Este documento explica as etapas de troubleshooting e isola qual parte ou componente de um Cisco 7200 estão falhando quando você identifica uma variedade de mensagens de erro de paridade. Nós recomendamos que você leia Troubleshooting Router Crashes and Processor Memory Parity Errors (PMPEs) antes de continuar a leitura deste documento.

Observação: as informações neste documento são baseadas nos Cisco 7200 Series Routers.

Prerequisites

Requirements

Não existem requisitos específicos para este documento.

Componentes Utilizados

Este documento não se restringe a versões de software e hardware específicas.

As informações neste documento foram criadas a partir de dispositivos em um ambiente de laboratório específico. All of the devices used in this document started with a cleared (default) configuration. Se você trabalhar em uma rede ativa, certifique-se de que entende o impacto potencial de qualquer comando antes de utilizá-lo.

Conventions

For more information on document conventions, refer to the Cisco Technical Tips Conventions.

Análise de árvore de falha de erro de paridade do Mecanismo de processamento de rede (NPE)

Este diagrama descreve as etapas para determinar que parte ou componente de um Cisco 7200 está falhando quando você identifica uma variedade de mensagens de erro de paridade.

Nota: Capture e grave os registros de saída e console show tech-support e colete todos os arquivos crashinfo durante eventos de erro de paridade.

Detecção e mensagens de erro de paridade de NPE

Esta seção contém diagramas de blocos do NPE e onde esses sistemas detectam erros de paridade. Você pode encontrar uma descrição de cada tipo de mensagem de erro abaixo.

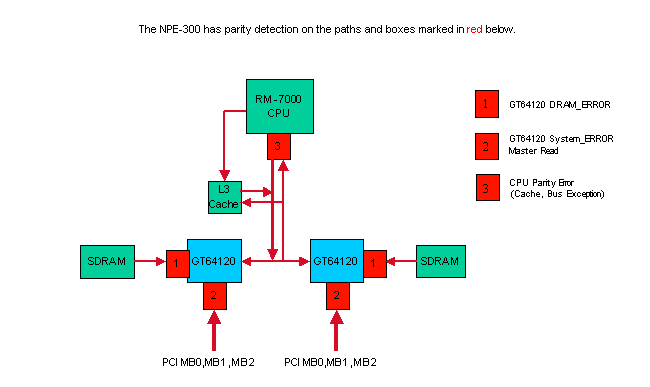

Erros de paridade no NPE-300

O NPE-300 usa a verificação de paridade na memória compartilhada (SDRAM), no barramento PCI e na interface externa da CPU para proteger o sistema contra o mau funcionamento por erros de bit. A verificação de paridade é capaz de detectar um único erro de bit utilizando um método simples; adicionando um bit de verificação por oito bits de dados. Se detectar um erro de bit ao passar os dados entre os componentes de hardware, o sistema descartará os dados errados. Os erros de bit único em qualquer local do diagrama acima fazem com que o roteador seja redefinido.

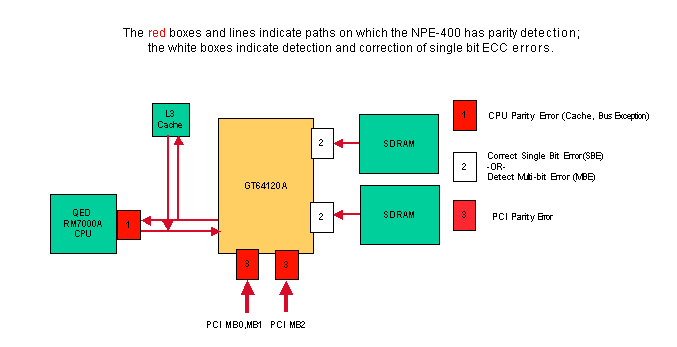

Paridade NPE-400/Detecção de ECC

O NPE-400 usa correção de erro de bit único e detecção de erro de vários bits ECC (correção de código de erro) para memória compartilhada (SDRAM). Para aumentar a disponibilidade do sistema no NPE-400, o ECC corrige erros de bit único na SDRAM, para permitir que o sistema opere normalmente sem redefinir e sem tempo de inatividade. Para obter mais informações sobre como o ECC melhora a disponibilidade do sistema, consulte a página Aumentando a disponibilidade da rede.

Um erro de vários bits na SDRAM faz com que o roteador seja redefinido com uma exceção de erro de cache ou erro de barramento. O restante da memória e dos barramentos no sistema usam detecção de paridade de bit único. Os erros de bit único em 1 e 3 no diagrama acima fazem com que o roteador seja redefinido.

Erros de paridade no roteador C7200

Vários dos dispositivos de verificação de paridade no roteador C7200/NPE podem relatar dados com paridade ruim para qualquer operação de leitura ou gravação. Aqui está uma descrição das várias mensagens de erro relatadas em um sistema C7200/NPE:

Erro de DRAM GT64010/GT64120

Esse erro é relatado quando um controlador de sistema GT64120 detecta um erro de paridade ao ler SDRAM:

%ERR-1GT64120 (PCI0):Fatal error, Memory parity error (external) GT=0xB4000000, cause=0x0100E283, mask=0x0ED01F00, real_cause=0x00000200 Bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x1C000000

Substitua a SDRAM após uma segunda falha. Se a falha persistir, substitua o NPE.

Nota: Para NPEs mais antigos (NPE-100/150/2000) que usam os controladores GT64010, o erro é semelhante a este:

%ERR-1-GT64010: Fatal error, Memory parity error (external) cause=0x0300E283, mask=0x0CD01F00, real_cause=0x00000200 bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x00000000

A controladora GT64010 usa RAM dinâmica (DRAM) e não SDRAM. Nesse caso, substitua a DRAM após uma segunda falha. Se a falha persistir, substitua o NPE.

Leitura mestre de erro de paridade do sistema GT64010/GT64120

Um erro de paridade na leitura principal é um erro de paridade disparado pelo acesso a uma ponte PCI (Peripheral Component Interconnect). Aqui está um exemplo de saída de erro de paridade:

%ERR-1-GT64120 (PCI0):Fatal error, Parity error on master read GT=B4000000, cause=0x0110E083, mask=0x0ED01F00, real_cause=0x00100000 Bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x00000470 %ERR-1-SERR: PCI bus system/parity error %ERR-1-FATAL: Fatal error interrupt, No reloading Err_stat=0x81, err_enable=0xFF, mgmt_event=0x40

Substitua o componente apropriado após uma segunda falha. O despejo da ponte do sistema indica qual componente substituir.

System bridge dump:

Bridge 1, for PA bay 1, 3 and 5. Handle=1

DEC21150 bridge chip, config=0x0

(0x1C):sec status, io base =0x83A09141

Detected Parity Error on secondary bus

Data Parity Detected on secondary bus

(0x20):mem base & limit =0x4AF04880

Essas tabelas informam qual componente tem um possível problema na saída da mensagem de erro.

NPE-100/150/200:

| Número da ponte | Para que serve a ponte? | Erro de paridade no barramento principal | Erro de paridade no barramento secundário |

|---|---|---|---|

| Ponte 0 | Downstream MB0 para MB1 0 | Substitua o NPE | Substituir o NPE; se ainda estiver presente, substitua o chassi |

| Ponte 1 | Upstream MB1 para MB0 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substitua o NPE |

| Ponte 2 | Downstream MB0 a MB2 | Substitua o NPE | Substituir o NPE; se ainda estiver presente, substitua o chassi |

| Ponte 3 | Upstream MB2 para MB0 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substitua o NPE |

NPE-175/225/300/400/NSE-1:

| Número da ponte | Para que serve a ponte? | Erro de paridade no barramento principal | Erro de paridade no barramento secundário |

|---|---|---|---|

| Ponte 0 | Para o compartimento PA 0 (placa de E/S, PCMCIA, interfaces | Substitua o NPE | Substituir o NPE; se ainda estiver presente, substitua a placa de E/S. Se ainda estiver presente, substitua o chassi |

| Ponte 1 | Para o compartimento PA 1, 3 e 5 | Substitua o NPE | Substituir o NPE; se ainda estiver presente, substitua o chassi |

| Ponte 2 | Para o compartimento PA 2, 4 e 6 | Substitua o NPE | Substituir o NPE; se ainda estiver presente, substitua o chassi |

Todos os C7200s:

| Número da ponte | Para que serve a ponte? | Erro de paridade no barramento principal | Erro de paridade no barramento secundário |

|---|---|---|---|

| Ponte 4 | Adaptador de porta 1 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substituir PA 1; se ainda estiver presente, substitua o chassi |

| Ponte 5 | Adaptador de porta 2 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substituir PA2; se ainda estiver presente, substitua o chassi |

| Ponte 6 | Adaptador de porta 3 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substituir PA3; se ainda estiver presente, substitua o chassi |

| Ponte 7 | Adaptador de porta 4 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substituir PA 4; se ainda estiver presente, substitua o chassi |

| Ponte 8 | Adaptador de porta 5 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substituir PA 5; se ainda estiver presente, substitua o chassi |

| Ponte 9 | Adaptador de porta 6 | Substituir o NPE; se ainda estiver presente, substitua o chassi | Substituir PA 6; se ainda estiver presente, substitua o chassi |

Erro de paridade da CPU

Como em todos os computadores e dispositivos de rede, o NPE é susceptível à rara ocorrência de erros de paridade na memória do processador. Os erros de paridade podem fazer com que o sistema seja redefinido e podem ser um Single Event Upset (SEU ou erro de software) transitório ou podem ocorrer várias vezes (geralmente chamados de erros de hardware) devido a danos no hardware. Para obter mais informações sobre SEUs, consulte a página Aumentando a disponibilidade da rede. Um erro de paridade da CPU é relatado se a CPU detectar um erro de paridade ao acessar qualquer um dos caches do processador (L1, L2 ou, se encaixado, L3).

Aqui estão quatro exemplos desse tipo de erro:

Exemplo 1:

Error: SysAD, data cache, fields: data, 1st dword

Physical addr(21:3) 0x195BE88,

Virtual address is imprecise.

Imprecise Data Parity Error

Imprecise Data Parity Error

O NPE tem um processador R7K com cache sem bloqueio. Cache sem bloqueio significa que quando executa uma instrução para carregar dados em um registro e esses dados não estão no cache L1, a CPU carrega os dados de um cache de ordem mais baixa ou dos dados SDRAM. A CPU não bloqueia a execução de instruções adicionais, a menos que haja outra falha de cache ou que outra instrução dependa dos dados sendo carregados. Isso pode acelerar muito o processador e melhorar o desempenho, mas também pode levar a erros de paridade a serem imprecisos. Um erro de paridade impreciso ocorre quando a CPU lê informações sem bloquear e, posteriormente, determina que houve um erro de paridade na linha de cache associada. O processador R7K não consegue nos dizer especificamente qual instrução estava sendo executada quando a linha de cache estava sendo carregada, e é por isso que chamamos isso de erro de paridade impreciso.

Mesmo que os sistemas usem a correção de código de erro (ECC), ainda é possível ver um erro de paridade ocasional quando mais de um erro ocorreu nos 64 bits de dados devido a um erro de hardware no cache.

Um erro de paridade ocorre quando um valor de bit de sinal é alterado de seu valor original (0 ou 1) para o valor oposto. Esse erro pode ocorrer devido a um erro de paridade suave ou difícil.

Os erros de paridade suave ocorrem devido a uma influência externa na memória do dispositivo, que altera o valor do bit no nível atual. Esse tipo de problema é transitório e não ocorre novamente. Os erros de paridade de hardware ocorrem quando o valor do bit é alterado pela própria memória devido a danos na memória. Nesse caso, o problema ocorre toda vez que essa área de memória é usada, o que significa que o problema pode se repetir várias vezes em alguns dias ou uma semana.

Exemplo 2:

Error: SysAD, instr cache, fields: data, 1st dword

Physical addr(21:3) 0x000000,

virtual addr 0x6040BF60, vAddr(14:12) 0x3000

virtual address corresponds to main:text, cache word 0

Low Data High Data Par Low Data High Data Par

L1 Data: 0:0xAE620068 0x8C830000 0x00 1:0x50400001 0xAC600004 0x01

2:0xAC800000 0x00000000 0x02 3:0x1600000B 0x00000000 0x01

Low Data High Data Par Low Data High Data Par

DRAM Data: 0:0xAE620068 0x8C830000 0x00 1:0x50400001 0xAC600004 0x01

2:0xAC800000 0x00000000 0x02 3:0x1600000B 0x00000000 0x01

Exemplo 3:

Cache Err Reg = 0xE4588D10 Data reference, Secondary/Sys intf cache, Data field error Error on 1st doubleword on System interface No errors in addition to instr error Data phy addr that caused last parity or bus error: 0x1E84040C

Exemplo 4 (apenas NPE-300 e NPE-400):

%CERF-3-RECOVER: PC=0x604F136C, Origin=L3 Data ,PhysAddr=0x013CEFD0

or

%SYS-2-CERF_ABORT: Reason=0xEE23, PC=0x604629C8, Origin=L3 Data, Phys Addr=0x0287A4E8

Ambas as mensagens acima são acompanhadas por um "relatório da função de recuperação de erros de cache (CERF)" da seguinte maneira:

CERFa[1 ] 05:25:36 MET Tue Jul 9 2002: result=0xEE23; instr_pos=-2; rpl_off=1 CERFb[1 ] PC =604629C8; ORGN=L3 Data; PRID=00002710; PHYA=0287A4E8 CERFc[1 ] SREG=3400E105; CAUS=00000400; DEA0=0287A4E8; ECC =00000000 CERFd[1 ] CERR=E447A4EA; EPC =606361F8; DEA1=02517058; INFO=00000000 CERFe[1 ] CACHE=28FF78B4 62B36D98 02020684 00000E17 00000030 00000001 61F2934C 3EDA025D CERFe[1 ] SDRAM=28FF78B4 62B36D98 02020684 00000E17 00000030 00000001 61F2934C 3EDA025D CERFg[1 ] CXT =00000000; XCXT=00000000; BVAD=00000008; PFCL=00000000 CERFh[1 ] ISeq: 0045182B; 1060000E; 2C4203E9; 92430028; 38420001; 30630005 CERFi[1 ] o0 $3 ....; beq....; sltiu $2 ....; lbu $3, 0x0028($18); xori $2....; andi $3 ....;* CERFj[1 ] ; ; ; 6287A4E8; ; ; CERFk[1 ] ResumptionCode= 0x92430028; 0x0000000F; 0x42000018 CERFl[1 ] Instr's checked=4; diags=0x00000158,0x00040000,3600,1,0 CERFm[1 ] BaseRegLost later/off: 0/0 times; StoredValueLost: 0 times CERFn[1 ] INFO=00000000; CNFG=5061F4BB; ICTL=00000000 Initial Register Values CERFs00[1 ] $0=00000000 AT=61A30000 v0=00000001 v1=00000002 CERFs04[1 ] a0=28FF8728 a1=00003A98 a2=00000000 a3=00000007 CERFs08[1 ] t0=00000000 t1=3400E101 t2=606381E0 t3=FFFF00FF CERFs12[1 ] t4=606381C8 t5=000005D4 t6=00000008 t7=61C50000 CERFs16[1 ] s0=6189C188 s1=00000000 s2=6287A4C0 s3=00003A98 CERFs20[1 ] s4=61BD57B0 s5=00000006 s6=00000000 s7=61BD6C60 CERFs24[1 ] t8=60634788 t9=00000000 k0=621A8374 k1=6063EA40 CERFs28[1 ] gp=61A33B20 sp=61E28678 s8=00000000 ra=60462CA4 1 Cache error exceptions already reported

Você verá os registros acima se CERF estiver habilitado em um NPE-300 ou NPE-400 e um erro de paridade ocorrer. Para obter mais informações sobre o CERF, consulte a seção Soluções abaixo.

Soluções

O seguinte curso de ação é recomendado quando você encontrar tais erros:

-

Monitore o hardware afetado para ver se o mesmo problema acontece novamente. Caso contrário, foi um evento único transitório (SEU) e você não precisa tomar nenhuma ação.

-

Caso o problema não ocorra novamente, o comando cache L3 bypass/disable é uma opção que pode ajudar a reduzir o impacto do problema. Esse comando está disponível somente nas seguintes plataformas:

-

7200 com mecanismo de processador NPE-300, NPE-400 ou NSE-1

-

7400 com mecanismo de processador NSE-1

Como o NPE-300 não suporta memória ECC, este recurso é especialmente importante para aumentar a disponibilidade do sistema e tratar esses erros de paridade sem interrupção do serviço. Isso resolve muitos erros de paridade de software. A advertência é que há um leve impacto no desempenho do sistema quando o cache L3 está desativado. A degradação do desempenho varia entre 1% e 10%, dependendo da configuração do sistema. A sintaxe para usar esse comando depende da versão do software Cisco IOS.

-

O comando cache L3 disable pode ser encontrado nas versões 12.3(5a) e posteriores do software Cisco IOS. Também estará disponível no artigo 12.1(22)E. Nessas versões, o cache L3 é desativado por padrão, portanto, não é necessária nenhuma ação para aproveitar esse recurso. O cache L3 pode ser reativado com o comando no cache L3 disable.

-

O comando cache L3 bypass pode ser encontrado nos Cisco IOS Software Releases 12.2(6)S, 12.2(6)B, 12.2(8)BC1b, 12.0(20)SP, 12.2(6)PB, 12.2(2)DD2, 12.0(20)ST3, 12.0(21)S, 12.1(11)EC, 12.2(7)T, 12.1(13) e 12.2(7) ou posterior e 12.1(11)E a 12.1(21)E. Esse comando é desativado por padrão.

Para ativar o desvio de cache L3, digite o seguinte no modo de configuração:

Router(config)#cache L3 bypass

Para desativar o desvio de cache L3, digite o seguinte no modo de configuração:

Router(config)#no cache L3 bypass

A nova configuração de cache não entrará em vigor até que o roteador seja recarregado.

Quando o roteador é inicializado, as informações do sistema são exibidas, incluindo informações sobre o cache L3. Isso ocorre porque o arquivo startup-config ainda não foi processado pelo sistema. Depois que o arquivo startup-config é processado, o cache L3 é ignorado se o comando cache L3 bypass estiver na configuração.

Para verificar a configuração do cache L3, execute o comando show version. Se o cache L3 for ignorado, não haverá referência ao cache L3 na saída show version.

-

-

Outro recurso que ajuda a aumentar a disponibilidade do sistema é o Cache Error Recovery Function (CERF). Quando esse recurso está ativado (esse é o padrão nas versões mais recentes do software Cisco IOS, mas a partir de fevereiro de 2004, somente para NPE-300 e NPE-400), o software Cisco IOS tenta resolver o erro de paridade e evitar que o processador falhe. Este recurso resolve cerca de 75% de certos tipos de erros de paridade suave. Ao chamar esse comando, o sistema vê uma degradação de desempenho inferior a 5%.

O CERF para o NPE-300 pode ser encontrado nos Cisco IOS Software Releases 12.1(15), 12.1(12)EC, 12.0(22)S, 12.2(10)S, 12.2(10)T, 12.2(10), 12.2(2)B4, 12.2(11)BC1b e 12.1(5)XM8 ou posterior.

CERF para o NPE-400 pode ser encontrado em 12.3(3)B, 12.2(14)S3, 12.1(20)E, 12.1(19)E1, 12.3(1a), 12.2(13)T5, 12.2(18)S, 2.3(2)T, 12.2(18), 12.3(3) e 12.3(1)B1 ou posterior.

O CERF para o NPE-300 requer a revisão de hardware 4.1 ou superior. Para identificar a versão de hardware do NPE-300, use o comando show c7200.

Router>show c7200 ... C7206VXR CPU EEPROM: Hardware revision 4.1 Board revision A0 ...

O CERF para o NPE-400 requer o processador R7K revisão 2.1 ou superior. Para identificar a revisão do processador do NPE-400, use o comando show version.

Router>show version ... cisco 7206VXR (NPE400) processor with 491520K/32768K bytes of memory. R7000 CPU at 350Mhz, Implementation 39, Rev 3.2, 256KB L2, 4096KB L3 Cache 6 slot VXR midplane, Version 2.1 ...

Observação: é importante coletar todos os arquivos relevantes de informação de travamento para determinar a causa raiz do erro, conforme explicado em Recuperando informações do arquivo Crashinfo.

Se as sugestões acima não resolverem o problema, a substituição do NPE pode ajudar em casos de ocorrências repetidas de erros de paridade, já que erros de paridade física são causados por hardware danificado. As substituições de hardware são idênticas ao NPE original. A substituição do NPE não garante que nenhum erro de paridade adicional ocorra, pois os SEUs (Single Event Upsets, upsets de eventos únicos) são inerentes a qualquer equipamento de computador com memória.

Informações Relacionadas

Histórico de revisões

| Revisão | Data de publicação | Comentários |

|---|---|---|

1.0 |

13-Apr-2009 |

Versão inicial |

Contate a Cisco

- Abrir um caso de suporte

- (É necessário um Contrato de Serviço da Cisco)

Feedback

Feedback