# Especificação de design de HSSI (Interface serial de alta velocidade)

## Contents

---

[Introdução](#)

[Pré-requisitos](#)

[Requisitos](#)

[Componentes Utilizados](#)

[Conventions](#)

[Aviso e Autores](#)

[Aviso](#)

[Autores conjuntos](#)

[Adendo HSSI Edição 1](#)

[Adenda #1](#)

[Adenda #2](#)

[Adenda #3](#)

[1.0 Uso Planejado](#)

[1.1 Organização de documentos](#)

[1.2 Comparação com padrões existentes](#)

[2.0 Termos e definições](#)

[3.0 Especificações elétricas](#)

[3.1 Definições de sinal](#)

[3.2 Características Elétricas](#)

[3.3 Operação à prova de falhas](#)

[3.4 Temporização](#)

[4.0 Especificação física](#)

[4.1 Física](#)

[4.2 Elétrico](#)

[4.3 Conector](#)

[4.4 Atribuição de pinos](#)

[Apêndice C: Imunidade a ruídos](#)

[Informações Relacionadas](#)

---

## Introdução

Este documento especifica a interface de camada física que existe entre um DTE, como, por exemplo, um roteador de alta velocidade ou dispositivo de dados similar, e um DCE, como o DS3 (44.736 Mbps) ou SONET STS-1 (51,84 Mbps) DSU.

# Pré-requisitos

## Requisitos

Não existem requisitos específicos para este documento.

## Componentes Utilizados

Este documento não se restringe a versões de software e hardware específicas.

## Conventions

Consulte as [Convenções de Dicas Técnicas da Cisco para obter mais informações sobre convenções de documentos.](#)

# Aviso e Autores

## Aviso

A cisco Systems, Incorporated e a T3plus Networking, Incorporated não fazem nenhuma declaração a respeito e não garantem nenhuma das informações da Especificação, mas as fornecem de boa fé e com o melhor de seu conhecimento e capacidade. Sem restringir a generalidade do precedente, a Cisco Systems e a T3plus Networking não fazem representações nem garantias quanto à adequação para uma finalidade específica, nem quanto ao uso das informações no sentido de que ele possa vir a infringir patentes ou outros direitos de qualquer pessoa. O receptor renuncia a qualquer reclamação que possa ter contra a Cisco Systems ou T3plus Networking, referente ao uso que o receptor faça das informações ou dos produtos aqui mencionados.

A permissão é concedida para reproduzir e distribuir esta especificação desde que:

- Os nomes cisco Systems, Inc. e T3plus Networking, Inc. aparecem como autores,

- uma cópia desse aviso aparece em todas as cópias,

- o conteúdo deste documento não é alterado nem modificado.

O conteúdo deste documento não poderá ser alterado ou modificado sem a expressa autorização por escrito da Cisco Systems e da T3plus Networking. Pretende-se que este documento sirva como uma especificação de interface serial de alta velocidade e evolua para um padrão da indústria. Com esta intenção, espera-se que esta Especificação possa ser revisada no futuro para refletir requisitos adicionais ou aderência a padrões nacionais ou internacionais à medida que eles evoluem. A Cisco Systems e a T3plus Networking reservam-se o direito de alterar ou modificar esta Especificação ou os equipamentos a que ela se relaciona a qualquer momento, sem aviso prévio e sem responsabilidade.

## Autores conjuntos

John T. Chapman

Cisco Systems, Inc.

1525 O'Brien Drive

Menlo Park, Ca 94025

jchapman@cisco.com

TEL: (415) 688-7651

Mitri Halabi T3plus Networking, Inc. mitri@t3plus.com 2840 San Tomas Expressway TEL: (408) 727-4545 Santa Clara, Ca, 95051 FAX: (408) 727-5151

Para receber cópias atualizadas dessa especificação, é aconselhável solicitar a sua adição na lista de distribuição da Especificação HSSI da Cisco Systems ou da T3plus Networking.

## Adendo HSSI Edição 1

Este é um conjunto de 3 adendos às especificações HSSI nas adições e esclarecimentos do documento desde a versão 2.11 e para aprimorar as capacidades de operação e diagnóstico dos DCEs (equipamentos de terminação de circuito de dados) e das DSUs (unidades de serviços de dados).

### Adenda #1

Exclua todas as referências a "clock must be maintained for n cycle after the last valid data" (O relógio deve ser mantido por n ciclos após os últimos dados válidos). É consistente com HSSI sendo uma especificação da camada 1 e, portanto, não tem conhecimento da validade dos dados.

Substituir pela seguinte frase:

"Para facilitar as várias implementações do multiplexador DCE de bit/byte/frame, o relógio pode conter uma defasagem para permitir a eliminação de pulsos de enquadramento e a limitação de largura de banda do HSSI.

O intervalo descontínuo máximo não foi especificado. No entanto, espera-se que as origens de relógio ST e RT sejam geralmente contínuas quando TA e CA são declarados. Um intervalo de intervalo é medido como a quantidade de tempo entre duas bordas de relógio consecutivas do mesmo declive.

A taxa de transferência de dados instantânea nunca deve exceder 52 Mbps.

### Adenda #2

Os resistores de 1,5 kohm devem ser usados em vez do resistor de 10 kohm para as funções pullup e pull down em todos os receptores. Isso permite que o mínimo de 150 mvolts apropriado seja desenvolvido nos resistores de terminação de 110 ohms.

## Adenda #3

Um sinal opcional, LC, foi adicionado do DCE ao Equipamento de Terminal de Dados (DTE) nos pinos 5 (+) e 30 (-) do par de sinais reservado. LC é um sinal de solicitação de loopback do DCE para o DTE, para solicitar que o DTE forneça um caminho de loopback para o DCE. Mais especificamente, o DTE definiria TT=RT e SD=RD. ST não seria usado e não poderia ser considerado como uma fonte de tempo válida nessas circunstâncias.

Isso permitiria que os diagnósticos de gerenciamento de rede DCE/DSU testassem a interface DCE/DTE independentemente do DTE. Segue a filosofia HSSI de que tanto o DCE quanto o DTE são correspondentes independentes inteligentes e de que o DCE é capaz de manter o próprio canal de comunicação de dados e ser responsável por ele.

Caso o DTE e o DCE confirmem solicitações de loopback, o DTE receberá preferência.

## 1.0 Uso Planejado

Este documento especifica a interface de camada física que existe entre um DTE, como, por exemplo, um roteador de alta velocidade ou dispositivo de dados similar, e um DCE, como o DS3 (44.736 Mbps) ou SONET STS-1 (51,84 Mbps) DSU. Extensões futuras a esta especificação podem incluir suporte para taxas de até SONET STS-3 (155,52 Mbps).

### 1.1 Organização de documentos

A Seção 1 apresenta a HSSI, relacionando-a a outras especificações. A seção 2 contém uma lista dos termos e definições utilizados no presente caderno de especificações. A seção 3 define as especificações elétricas, inclusive nomes de sinal, definições, características, operação e cronometragem. A seção 4 descreve as propriedades físicas incluindo tipos de conector, tipos de cabo e atribuições de pinos. O Apêndice A relaciona graficamente as relações de temporização. O Apêndice B define graficamente as convenções de polaridade. O Apêndice C tem uma análise detalhada da imunidade a ruídos de ECL.

### 1.2 Comparação com padrões existentes

Essa especificação é diferente das séries de padrões ANSI/EIA, EIA-232-D, EIA-422-A, EIA-423-A, EIA-449 e EIA-530 porque ela:

- suporta taxas de bits seriais até 52 Mbps

- usa níveis de transmissão de Lógica acoplada por emissor (ECL)

- permite que os sinais de cronometragem tenham gaps, isto é, sejam descontínuos

- usa um protocolo de sinal de controle simplificado

- usa um protocolo de sinal de loopback mais detalhado

- usa um conector diferente

## 2.0 Termos e definições

Essa especificação atende às seguintes definições:

Loopback analógico:

Um loopback em qualquer direção associado ao lado da linha de um DCE.

Asserção:

O (+lado) de um dado sinal estará em Voh potencial enquanto o (-lado) do mesmo sinal estará em Vol potencial (ref: seção 3.2 e Apêndice B)

Desassserção:

O (lado+) de um determinado sinal estará em no possível Vol enquanto o (lado-) do mesmo sinal estará no possível Voh.

Canal de comunicações de dados:

O meio de transmissão e o equipamento de interferência envolvido na transferência de informações entre DCEs. Nesta especificação, presume-se que o canal de comunicação de dados seja full duplex.

DCE:

Data Communications Equipment (Equipamento de comunicações de dados). Os dispositivos e as conexões de uma rede de comunicação que conecta o canal de comunicação de dados ao dispositivo final (DTE). Isso será usado para descrever o CSU/DSU.

Loopback digital:

Um loopback em qualquer direção associado à porta DTE de um DCE.

DS3:

Nível 3 do sinal digital. Também conhecido como T3. Equivalente em largura de banda a 28 T1. A taxa de bit é 44.736 Mbps.

DSU:

Data Service Unit (Unidade de Serviço de Dados). Fornece ao DTE acesso a recursos de telecomunicações digitais.

DTE:

Data Terminal Equipment (Equipamento Terminal de Dados). A parte de uma estação de dados que serve como origem, destino ou ambos de dados e que fornece função de controle de comunicação de dados de acordo com os protocolos. Isso será usado para descrever um roteador ou dispositivo semelhante.

Relógio Interrompido:

Um fluxo de relógio a uma taxa de bits nominal que pode estar sem pulsos de relógio em intervalos arbitrários por períodos arbitrários.

OC-N:

O sinal óptico resultante de uma conversão óptica de um sinal STS-N.

SONET:

Synchronous Optical Network (Rede Ótica Síncrona). Um padrão ANSI/CCITT para padronizar o uso de sistemas de comunicação óptica.

STS-N:

Nível n do sinal de transporte síncrono n, em que  $n = 1,3,9,12,18,24,36,48$ . O STS-1 é o sinal lógico básico para o SONET com uma taxa de 51,84 Mbps. STS-N são obtidos por sinais N STS-1 de intercalação de byte juntamente com uma taxa de N vezes 51,84 Mbps.

## 3.0 Especificações elétricas

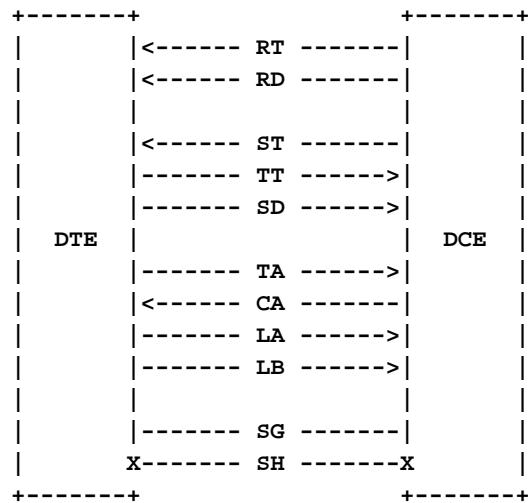

### 3.1 Definições de sinal

RT: Receive Timing (Tempo de recepção)

Direção: de DCE

RT é um relógio gapped com uma taxa de bits máxima de 52 Mbps e fornece informações sobre cronometragem do elemento de sinal a RD.

RD: Receber Dados

Direção: de DCE

Os sinais de dados gerados pelo DCE, em resposta aos sinais de linha do canal de dados recebidos de uma estação de dados remota, são transferidos nesse circuito para o DTE. O RD está sincronizado com o RT.

ST: Tempo de envio

Direção: de DCE

ST é um relógio com gaps com uma taxa de bits máxima de 52 Mbps e fornece informações sobre cronometragem do elemento de sinal de transmissão ao DTE.

TT: Temporização do terminal

Direção: para DCE

O TT fornece informações sobre cronometragem do elemento de sinal de transmissão ao DCE. TT é o sinal ST ecoado para o DCE pelo DTE. Apenas o DTE deve colocar o TT em buffer; o TT não deve estar bloqueado com nenhum outro sinal.

SD: Enviar Dados

Direção: para DCE

Os sinais de dados originados pelo DTE, para serem transmitidos pelo canal de dados a uma estação de dados distante. O SD está sincronizado com o TT.

TA: dados Equipamento terminal disponível

Direção: para DCE

O TA será declarado pelo DTE, independentemente do CA, quando o DTE estiver preparado tanto para enviar quanto para receber dados de e para o DCE. A transmissão de dados não deve começar até que CA também tenha sido declarada pelo DCE.

Se o canal de comunicações de dados exigir um padrão de dados keep alive quando o DTE é desconectado, o DCE deve fornecer esse padrão enquanto o TA é desafirmado.

CA: Equipamento de comunicações de dados disponível

Direção: de DCE

A CA será declarada pelo DCE, independentemente do TA, quando o DCE estiver preparado para enviar e receber dados de e para o DTE. Indica que o DCE obteve um canal de comunicação de dados válido. A transmissão de dados não deve começar até que o TA também tenha sido declarado pelo DTE.

LA: Circuito de loopback A

LB: Circuito de loopback B

Direção: para DCE

LA e LB são declarados pelo DTE para fazer com que o DCE e seu canal de comunicação de dados associado forneçam um dos três modos de loopback de diagnóstico. Especificamente,

- LB = 0, LA = 0: sem loopback

- LB = 1, LA = 1: loopback DTE local

- LB = 0, LA = 1: loopback de linha local

- LB = 1, LA = 0: loopback de linha remota

Um 1 representa asserção e um 0 representa desassserção.

Um loopback DTE (digital) local ocorre na porta DTE do DCE e é usado para testar o link entre o DTE e o DCE. Um loopback de linha local (análogo) ocorre na porta lateral da linha do DCE e é usado para testar a funcionalidade do DCE. Um loopback de linha remota (análogo) ocorre na porta de linha do DCE remoto e é usado para testar a funcionalidade do canal de comunicação de dados. Há três loopbacks iniciados nessa seqüência. O DCE remoto é testado pelo comando remoto dos loopbacks locais. Observe que LA e LB são superconjuntos diretos dos sinais EIA LL (Loopback local) e RL (Loopback remoto).

O DCE local continua a reforçar CA durante todos os três modos de circuito de retorno. O DCE remoto negará o CA quando um loopback remoto estiver em efeito. Se o DCE remoto puder detectar um loopback local no DCE local, o DCE remoto desconfirmará sua CA; caso contrário, o DCE remoto confirmará sua CA quando houver um loopback local no DCE local.

O DCE implementa o loopback apenas para o DTE de comando. Os dados recebidos do canal de comunicações de dados são ignorados. Enviar dados para o canal de comunicações de dados é preenchido com o fluxo de dados de envio do DTE de comando ou com um padrão de dados de manutenção de atividade, dependendo dos requisitos específicos do canal de comunicações de dados.

Não há sinal explícito de status do hardware para indicar que o DCE entrou no modo de loopback. O DTE espera por um período de tempo apropriado após confirmar LA e LB antes de assumir que o loopback é válido. A quantidade apropriada de tempo depende do aplicativo e não faz parte desta especificação.

O modo de loopback aplica-se aos sinais de cronometragem e de dados. Assim, no enlace DTE - DCE, o mesmo sinal de temporização poderia atravessar o enlace três vezes, primeiro como ST, depois como TT e, finalmente, como RT.

SG: Sinal terra

Direção: Não aplicável

SG significa uma conexão com base de circuito em ambas as extremidades. O SG garante que os níveis de sinal de transmissão permaneçam dentro do intervalo de entrada no modo comum

dos receptores.

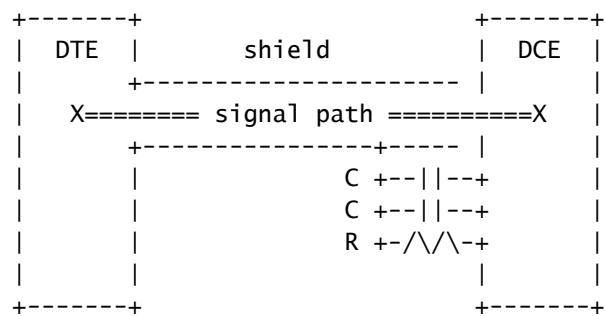

SH: Blindagem

Direção: Não aplicável

O protetor encapsula o cabo para propósitos de EMI e não está implicitamente planejado para transportar correntes de retorno de sinal. A blindagem é conectada diretamente ao aterramento do quadro DTE e pode escolher uma das duas opções no aterramento do quadro DCE. A primeira opção é conectar o protetor diretamente à base da estrutura DCE. A segunda opção é conectar a blindagem ao aterramento de quadro DCE através de uma combinação paralela de um capacitor cerâmico monolítico de 470 ohm, +/- 10%, resistor de 1/2 watt, 0,1 uF, +/- 10%, 50 volts e um capacitor cerâmico monolítico de 0,01 uF, +/- 10%, 50 volts. Isso é mostrado abaixo:

A rede R-C-C deve estar localizada o mais perto possível da junção blindagem/chassi. Como a blindagem é terminada diretamente nos chassis DTE e DCE, a blindagem não recebe uma atribuição de pinos dentro do conector. A continuidade de blindagem entre os cabos de conexão é mantida pelo invólucro do conector.

### 3.2 Características Elétricas

Todos os sinais são平衡ados, dirigidos diferencialmente e recebidos em níveis ECL padrão. A tensão de alimentação negativa de ECL, Vee, pode ser -5.2 Vdc +/- 10% ou -5.0 Vdc +/- 10% em qualquer uma das extremidades. Tempos de elevação e tempos de queda são medidos em níveis de limite de 20% a 80%.

#### TRANSMITTER:

|                    |                                                                          |         |         |     |

|--------------------|--------------------------------------------------------------------------|---------|---------|-----|

| driver type:       | ECL 10KH with differential outputs<br>(MC10H109, MC10H124 or equivalent) |         |         |     |

| signal levels:     | minimum                                                                  | typical | maximum |     |

| Voh:               | -1.02                                                                    | -0.90   | -0.73   | Vdc |

| Vol:               | -1.96                                                                    | -1.75   | -1.59   | Vdc |

| Vdiff:             | 0.59                                                                     | 0.85    | 1.21    | Vdc |

| trise:             | 0.50                                                                     | -       | 2.30    | ns  |

| tfall:             | 0.50                                                                     | -       | 2.30    | ns  |

| transmission rate: | 52 Mbps maximum                                                          |         |         |     |

| signal type:       | electrically balanced with Non Return to Zero                            |         |         |     |

(NRZ) encoding.

termination: 330 ohms low inductance resistance from each side to Vee.

RECEIVER:

- receiver type: ECL 10KH differential line receiver (MC10H115, MC10H116, MC10H125, or equivalent)

- termination: 110 ohms (carbon composition) differential, 5 Kohms common-mode (optional)

- min. signal level: 150 mvolts peak-to-peak differential

- max. signal level: 1.0 volt peak-to-peak differential

- common mode input range: -2.85 volts to -0.8 volts (-0.5 volts max)

Os valores se aplicam a uma faixa de temperatura ambiente de 0 a 75 graus Celsius e foram ajustados para a faixa Vee mais ampla.

### 3.3 Operação à prova de falhas

Caso o cabo de interface não esteja presente, os receptores ECL diferenciais devem assumir um estado conhecido como padrão. Para garantir isso, ao utilizar o 10H115 ou 10H116 coloque dois resistores de pull-up de 10 kohm +/- 1% sendo um no lado positivo e outro no negativo do receptor. Isso criará uma terminação longitudinal de 5 quilohms. O estado padrão de todos os sinais de interface é deasserted.

Não é necessário usar resistores externos ao usar o 10H125, uma vez que ele tem uma rede interna de polarização que forçará um estado de saída baixo quando as entradas são deixadas flutuantes.

A interface não deve estar danificada por uma conexão de circuito aberto ou de curto-circuito em qualquer combinação de pinos.

### 3.4 Temporização

A cronometragem de origem é definida como ondas de cronometragem geradas em um transmissor. A temporização de destino é definida como formas de onda de temporização incidentes em um receptor. Larguras de pulso são medidas entre 50% de pontos da amplitude final de pulso. A margem principal do pulso de sincronização deve ser definida como limite entre a negação e a asserção. A borda precedente do pulso de sincronização deve ser definida como o limite entre asserção e negação. A largura mínima do pulso de sincronização de origem positivo de RT, TT e ST deve ser de 7,7 ns. Isto permite uma tolerância de ciclo de serviço de origem de +/- 10%. Este valor é obtido de:

$$10\% = ((9.61 \text{ ns} - 7.7 \text{ ns}) / 19.23 \text{ ns}) \times 100\%$$

where:

$$19.23 \text{ ns} = 1 / (52 \text{ Mbps})$$

$$9.61 \text{ ns} = 19.23 \text{ ns} * 1/2 \text{ cycle}$$

Os dados passarão para o novo estado dentro de +/- 3 ns da borda dianteira do pulso de

cronometragem de origem.

A largura mínima do pulso de sincronização de destino positivo de RT, TT e ST deve ser de 6,7 ns. Os dados serão alterados para seu novo estado dentro de +/- 5 ns da borda de liderança do pulso de temporização de destino. Esses números permitem elementos de distorção de transmissão de 1.0 ns de distorção de largura de pulso e 2.0 ns de desvio entre tempo e dados. Isso deixa 1,7 ns para o tempo de configuração do receptor.

Os dados serão considerados válidos na ponta da trilha. Então, os transmissores cronometram os dados na borda precedente, e os receptores cronometram dados na borda posterior. Isso permite uma janela de aceitação para erro de desvio de dados do relógio.

O atraso do porto ST para o porto TT no DTE deve ser inferior a 25 ns. O DCE deve ser capaz de tolerar um retardo de pelo menos 100 ns entre a porta ST e a porta TT. Isso permite um atraso de 75 ns para 15 metros de cabo.

RT e ST podem ser gaps. Caso se tornem desativados pelo DCE, a desativação do RT não deve ocorrer até 23 pulsos de relógio após os últimos dados válidos em RD, e a desativação do ST não deve ocorrer até 1 pulso de relógio após os últimos dados válidos em SD. A definição de dados válidos depende do aplicativo e não está sujeita ao aplicativo.

CA e TA são assíncronos um do outro. Após a asserção de CA, os sinais ST, RT e RD não serão considerados válidos por pelo menos 40 ns. Na declaração de TA, os sinais TT e SD não serão considerados válidos por pelo menos 40 ns. Isso é planejado para permitir o tempo de configuração suficiente para a finalização de recebimento.

O TA não deve ser confirmado até pelo menos um pulso do relógio, depois que o último bit de dados no SD tiver sido transmitido. Isso não se aplica a CA, pois os dados são transparentes para DCE.

## 4.0 Especificação física

O cabo que conecta o DCE e o DTE consiste em 25 pares trançados com um protetor total de folha metálica/trance. Os dois conectores do cabo são machos. O DTE e o DCE possuem receptáculos fêmea. As dimensões são dadas em metros (m) e pés (pés).

### 4.1 Física

|              |                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| cable type:  | multi-conductor cable, consisting of 25 twisted pairs cabled together with an overall double shield and PVC jacket                      |

| gauge:       | 28 AWG, 7 strands of 36 AWG, tinned annealed copper, nominal 0.015 in. diameter                                                         |

| insulation:  | polyethylene or polypropylene; 0.24 mm, .0095 in. nominal wall thickness; 0.86 mm +/- 0.025 mm, .034 in. +/- 0.001 in. outside diameter |

| foil shield: | 0.051 mm, 0.002 in. nominal aluminum/polyester/aluminum laminated tape spiral wrapped around the cable core with a 25% minimum overlap  |

|                      |                                                                              |  |

|----------------------|------------------------------------------------------------------------------|--|

| braid shield:        | braided 36 AWG, tinned plated copper in accordance with 80% minimum coverage |  |

| jacket:              | 75 degrees C flexible polyvinylchloride                                      |  |

| jacket wall:         | 0.51 mm, 0.020 in. minimum thickness                                         |  |

| dielectric strength: | 1000 VAC for 1 minute                                                        |  |

| outside diameter:    | 10.41 mm +/- 0.18 mm, 0.405 in. +/- 0.015 in.                                |  |

| agency compliance:   | CL2, UL Subject 13, NEC 725-51(c) + 53(e)                                    |  |

| manufacturer p/n:    | QUINTEC (Madison Cable 4084)<br>ICONTEC RTF-40-25P-2 (Berk-tek, C&M)         |  |

## 4.2 Elétrico

|                                   |            |                      |

|-----------------------------------|------------|----------------------|

| maximum length:                   | 15 m       | 50 ft                |

| nominal length:                   | 2 m        | 6 ft                 |

| maximum DCR at 20 C:              | 23 ohms/km | 70 ohms/1000ft       |

| differential impedance at 50 MHz: |            |                      |

| nominal: (95% or more pairs)      | 110 ohms   | (+/- 11 ohms)        |

| maximum:                          | 110 ohms   | (+/- 15 ohms)        |

| signal attenuation at 50 MHz:     | 0.28 dB/m  | 0.085 dB/ft          |

| mutual capacitance within pair,   |            |                      |

| minimum:                          | 34 pF/m    | 10.5 pF/ft           |

| nominal: (95% or more pairs)      | 41 pF/m    | 12.5 pF/ft (+/- 10%) |

| maximum:                          | 48 pF/m    | 15.0 pF/ft           |

| capacitance, pair to shield,      |            |                      |

| maximum:                          | 78 pF/m    | 24 pF/ft             |

| delta:                            | 2.6 pF/m   | 0.8 pF/ft            |

| propagation delay,                |            |                      |

| maximum: (65% of c)               | 5.18 ns/m  | 1.58 ns/ft           |

| delta:                            | 0.13 ns/m  | 0.04 ns/ft           |

## 4.3 Conector

|                      |                                                                                                                                       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| plug connector type: | 2 row, 50 pin, shielded tab connectors<br>AMP plug part number 749111-4 or equivalent<br>AMP shell part number 749193-2 or equivalent |

| receptacle type:     | 2 row, 50 pin, receptical header with rails and latch blocks. AMP part number 749075-5, 749903-5 or equivalent                        |

## 4.4 Atribuição de pinos

| Signal Name | Dir. | Pin # (+side) | Pin # (-side) |

|-------------|------|---------------|---------------|

|-------------|------|---------------|---------------|

|                         |     |         |         |

|-------------------------|-----|---------|---------|

| SG - Signal Ground      | --- | 1       | 26      |

| RT - Receive Timing     | <-- | 2       | 27      |

| CA - DCE Available      | <-- | 3       | 28      |

| RD - Receive Data       | <-- | 4       | 29      |

| - reserved              | <-- | 5       | 30      |

| ST - Send Timing        | <-- | 6       | 31      |

| SG - Signal Ground      | --- | 7       | 32      |

| TA - DTE Available      | --> | 8       | 33      |

| TT - Terminal Timing    | --> | 9       | 34      |

| LA - Loopback circuit A | --> | 10      | 35      |

| SD - Send Data          | --> | 11      | 36      |

| LB - Loopback circuit B | --> | 12      | 37      |

| SG - Signal Ground      | --- | 13      | 38      |

| 5 ancillary to DCE      | --> | 14 - 18 | 39 - 43 |

| SG - Signal Ground      | --- | 19      | 44      |

| 5 ancillary from DCE    | <-- | 20 - 24 | 45 - 49 |

| SG - Signal Ground      | --- | 25      | 50      |

Os pinos 5&30, 14&30 a 18&43 e 20&45 a 24&49 são reservados para uso futuro. Para permitir compatibilidade com versões futuras, nenhum sinal ou receptor de qualquer tipo deve ser conectado a esses pinos.

(Apêndices A&B não disponíveis)

## Apêndice C: Imunidade a ruídos

Este apêndice calcula a imunidade a ruído dessa interface. Os 150 mvolts normais especificados de imunidade a ruído para 10KH ECL não são aplicáveis aqui porque as entradas diferenciais não utilizam Vbb de polarização de ECL interno.

As margens de ruído do modo comum (NMcm) e do modo diferencial (NMdiff) para os receptores de linha diferencial 10H115 e 10H116 são:

$$NMcm+ = Vcm_{max} - Voh_{max} = -0.50 \text{ Vdc} - (-0.81 \text{ Vdc}) = 310 \text{ mVdc}$$

$$NMcm- = Vol_{min} - Vcm_{min} = -1.95 \text{ Vdc} - (-2.85 \text{ Vdc}) = 900 \text{ mVdc}$$

$$\begin{aligned} NMdiff &= Vod_{min} * length * attenuation/length - Vid_{min} \\ &= 10^{((20\log(.59) - 50(.085))/20)} - 150 \text{ mv} = 361 \text{ mv} \\ \text{in dB:} \\ &= 20\log(.361) - 20\log(.15) \end{aligned}$$

As voltagens estão em 25°C. Vcm\_max foi escolhido para ser 100 mv abaixo do ponto de saturação Vih = -0,4 volts.

O receptor diferencial 10H125 tem uma alimentação de +5 Vdc e pode lidar com uma maior excursão positiva em sua entrada. O desempenho da margem de ruído do 10H125 é:

$$NMcm+ = Vcm_{max} - Voh_{max} = 1.19 \text{ Vdc} - (-0.81 \text{ Vdc})$$

NMcm- e NMdiff são os mesmos para todas as partes. Para permitir o uso de todos os receptores, o pior caso de ruído de modo comum no receptor deve estar limitado a 310 mvdc.

Interprete o intervalo de modo comum, Vcm\_max a Vcm\_min, como o intervalo máximo de voltagens absolutas que podem ser aplicadas à entrada do receptor, independentemente da voltagem diferencial aplicada. A faixa de tensão de sinal, Voh\_max to Vol\_min, representa a faixa máxima de tensões absolutas que o transmissor produzirá. A diferença entre essas duas faixas representa as margens comuns de ruído de modo, NMcm+ e NMcm-, em que NMcm+ é a excursão máxima para ruído de modo comum de adição, e NMcm- é a excursão máxima para o ruído de modo comum de subtração.

Com cinco pares trançados de terra de 50 pés, a quantidade de corrente de loop de terra necessária para usar até a margem de ruído no modo comum é:

$$\begin{aligned} I_{ground} &= NMcm+ / (\text{cable\_resistance}/5 \text{ pairs}) \\ &= (310 \text{ mVdc}) / (70 \text{ mohms/foot} \times 50 \text{ feet} / 10 \text{ wires}) \\ &= 0.9 \text{ amps dc} \end{aligned}$$

Este valor de corrente nunca deveria estar presente sob condições normais de operação.

O ruído do modo comum terá um efeito negligenciável na margem de ruído diferencial, Vdf\_app. Em vez disso, o Vdf\_app seria afetado pelo ruído sendo introduzido por um lado dos trilhos de energia no transmissor. A Vcc ECL tem uma razão de rejeição da fonte de alimentação (PSRR) de 0 dB, enquanto a Vcc ECL tem uma PSRR da ordem de 38 dB. Portanto, para reduzir o ruído diferencial, Vcc é aterrado e Vee é conectado a uma fonte de alimentação negativa.

## Informações Relacionadas

- [Página de suporte aos protocolos de roteamento IP](#)

- [Página de Suporte do IP Routing](#)

- [Suporte Técnico e Documentação - Cisco Systems](#)

## Sobre esta tradução

A Cisco traduziu este documento com a ajuda de tecnologias de tradução automática e humana para oferecer conteúdo de suporte aos seus usuários no seu próprio idioma, independentemente da localização.

Observe que mesmo a melhor tradução automática não será tão precisa quanto as realizadas por um tradutor profissional.

A Cisco Systems, Inc. não se responsabiliza pela precisão destas traduções e recomenda que o documento original em inglês (link fornecido) seja sempre consultado.