Cisco ONS 15454의 타이밍 및 동기화

목차

소개

이 문서에서는 Cisco ONS 15454에서 타이밍 및 동기화를 계획하는 지침을 제공합니다.

사전 요구 사항

요구 사항

다음 주제에 대한 지식을 보유하고 있으면 유용합니다.

-

Cisco ONS 15454

사용되는 구성 요소

이 문서의 정보는 다음 소프트웨어 및 하드웨어 버전을 기반으로 합니다.

-

Cisco ONS 15454

이 문서의 정보는 특정 랩 환경의 디바이스를 토대로 작성되었습니다.이 문서에 사용된 모든 디바이스는 초기화된(기본) 컨피그레이션으로 시작되었습니다.현재 네트워크가 작동 중인 경우, 모든 명령어의 잠재적인 영향을 미리 숙지하시기 바랍니다.

표기 규칙

문서 규칙에 대한 자세한 내용은 Cisco 기술 팁 표기 규칙을 참고하십시오.

배경 정보

이 제품에는 다음이 포함됩니다.

-

ANSI/SONET(American National Standards Institute/Synchronous Optical NETwork) 프로비저닝 플랫폼

-

European Telecommunication Standards Institute/International Telecommunications Union/Synchronous Digital Hierarchy(ETSI/ITU/SDH) 프로비저닝 플랫폼

-

전송 플랫폼, DWDM(Dense Wavelength Division Multiplexing)

이 문서의 타이밍 정보는 두 프로비저닝 플랫폼에 적용됩니다.전송 플랫폼은 타이밍을 통해 사용합니다.타이밍을 통해 수신되는 "east" 신호는 전송된 "west" 신호에, 수신되는 "west" 신호는 전송된 "east" 신호에 의해 시간 지정됩니다.

타이밍 아키텍처

TCC(Timing, Communications and Control) 카드와 XC(Cross Connect) 카드는 SONET/SDH 장비에 대한 업계 표준을 기반으로 ONS 15454의 타이밍 기능을 제어합니다.이중 TCC 및 XC 카드를 사용하여 내결함성 공통 시스템 하드웨어를 제공합니다.

참고: 이 문서에서는 일반적으로 TCC를 사용하여 TCC 카드의 모든 변형을 참조하고, XC는 XC 카드의 모든 변형을 참조합니다.

ANSI 섀시에는 포트에 두 개의 BITS(Building Integrated Timing Supply)가 있습니다.두 포트 모두 AIP(Auxiliary Interface Protection)에서 종료됩니다. AIP의 종료를 통해 활성 TCC 카드와 대기 TCC 카드가 모두 BITS를 모니터링할 수 있으며, 전원 서지 때문에 백플레인이 손상된 경우에도 BITS를 적절하게 종료할 수 있습니다.ETSI 플랫폼의 경우 BITS 인터페이스는 FMEC(Front Mount Electrical Connection) 패널에 있습니다.

모든 동기식 인터페이스(광 포트)는 TCC 카드가 관리하는 시스템 타이밍 참조에서 전송 타이밍을 도출합니다.XC 카드는 각 포트에 대한 전송 타이밍을 제공합니다.TCC는 다음과 같은 동기화 기능을 수행합니다.

-

참조를 모니터링, 자격 심사 및 선택합니다.

-

활성 참조를 필터링하고 잠급니다.

-

시스템 시계의 분포를 관리합니다.

-

2개의 BITS 입력을 종료합니다.

-

2개의 BITS 출력을 생성합니다.

-

SSM(동기화 상태 메시징)을 처리하고 생성합니다.

-

유지 관리를 위해 참조를 전환합니다.

-

동기화 경보 보고서를 생성하려면

시간 분포

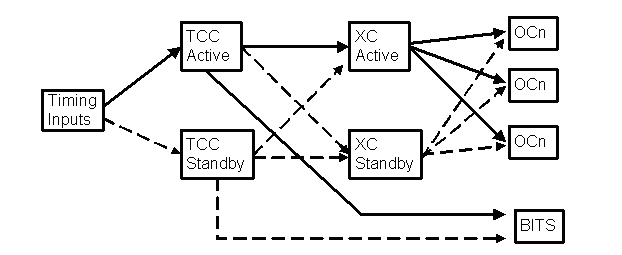

그림 1은 ANSI 시스템 내에서 타이밍 분산 방식을 나타냅니다.SDH 버전은 비슷하지만 간단한 용어가 변경되었습니다.이 섹션에서는 ANSI 버전을 예로 사용합니다.

참고: 실선은 활성 타이밍 분포를 나타내고, 대시 선은 대기 시간 분포를 나타냅니다.

그림 1 - ONS 15454 ANSI의 타이밍 선택 및 분포

각 시스템은 타이밍 프로비저닝을 기준으로 여러 형식의 입력 또는 참조 시계를 사용할 수 있습니다.사용 가능한 타이밍 입력은 BITS 1 및 2, 옵티컬 라인 및 내부 진동자입니다.이 모든 입력은 활성 TCC 카드의 타이밍 만 사용되지만 두 TCC 카드에 모두 제공됩니다.프로비저닝을 사용하여 최대 3개의 입력을 참조 클럭으로 지정할 수 있습니다.각 TCC 카드 내의 타이밍 회로는 독립적으로 자격을 심사하고 세 개의 참조 중 하나의 활성 참조를 선택하고 해당 참조에 잠금을 설정합니다.결과 시계를 시스템 시계 또는 NE 시계라고 합니다.

참고: 두 TCC 카드는 서로 잠기지 않습니다.

각 TCC 카드의 시스템 클럭은 모든 OCn 카드에 클럭을 공급하는 두 XC 카드에 분산됩니다.활성 XC 카드의 시계가 선택됩니다.

참고: SDH 플랫폼에서 타이밍은 TCC 카드에서 내부 버스를 통해 라인 카드로 직접 분배됩니다.

다른 시계를 운전하기 위해 TCC 카드도 회선에서 BITS 시계를 생성할 수 있습니다.

참고: BITS Out 클럭은 BITS 타이밍 루프를 방지하기 위해 클럭의 BITS에서 직접 파생될 수 없습니다.

타이밍 회로

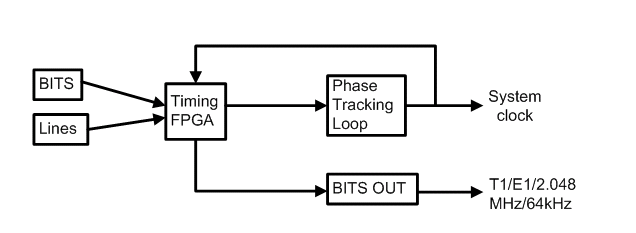

TCC 카드의 타이밍 회로는 모든 타이밍 관련 기능을 처리합니다.그림 2는 하이 레벨 흐름을 보여줍니다.무결성을 확인하기 위해 FPGA(Timing Field Programmable Gate Array)는 타이밍 입력을 처리합니다.시스템 시계는 비교의 참조로 사용됩니다.선택한 활성 참조는 시스템 시계(NE 시계)를 생성하는 단계 추적 루프에 입력됩니다.회선에서 오는 신호에 대해 BITS 신호를 생성하여 외부 장치에 타이밍(BITS Out)을 제공할 수도 있습니다.BITS Out 포트는 다양한 신호를 지원하는 2개의 금속 인터페이스를 제공합니다.

그림 2 - TCC의 타이밍 회로

참조 자격 심사 및 실패

활성 참조 선택에 영향을 주는 두 가지 방법이 있습니다.

-

프로비저닝

-

참조 자격

프로비저닝된 참조 클럭만 선택 프로세스의 후보가 됩니다.한 가지 예외는 내부 클럭입니다. 이는 다른 모든 참조가 실패할 경우 항상 기본 클럭입니다.그러나 프로비저닝된 참조를 활성 참조로 선택할 필요는 없습니다.선택한 참조는 자격 심사 프로세스를 통과해야 합니다.

각 참조는 상태 변경을 위해 5밀리초마다 폴링됩니다.30초 이상 TCC는 각 참조에 대한 빈도와 유더를 계산합니다.주파수 오프셋이 + 12.9ppm 이내인 경우(수락용) 참조가 검증됩니다.주파수가 유효한 주파수 범위(활성 BITS의 경우 15ppm, 활성 선의 경우 16ppm, 비활성 참조의 경우 13.1ppm)를 벗어나면 참조가 불량(거부)으로 표시되고 유다는 임계값(2ppm)을 초과하게 됩니다.경보가 수신되거나 신호가 없는 경우에도 참조가 불량으로 표시됩니다.경보는 LOS(Loss of Signal), LOF(Loss of Frame) 또는 AIS(Alarm Indication Signal)일 수 있습니다. 활성 참조가 실패하면 다음 최상의 참조로 선택하고 전환됩니다.

회선 동기화 참조를 제공하기 위해 프로비저닝된 IO 카드는 수신된 신호를 지속적으로 모니터링합니다.포트가 LOS, LOF 또는 AIS 상태이면 카드가 TCC에 대한 참조를 끕니다.따라서 TCC는 포트에서 참조를 불량으로 선언합니다.이 참조가 현재 활성 참조인 경우 다음 최상의 참조가 활성 참조가 됩니다.

수신 클럭에 SSM이 연결되어 있으면 참조 선택에 SSM이 사용됩니다.SSM 사용 여부에 관계없이 최고 품질 시계가 항상 활성 클럭으로 선택됩니다.동일한 품질을 가진 참조가 두 개 이상 있는 경우 우선순위가 가장 높은 참조(프로비저닝을 기준으로)가 활성 참조로 선택됩니다.

요약하면, 다음 조건 중 하나라도 참일 경우 참조는 수락되지 않습니다.

-

옵티컬 또는 BITS 입력은 LOS, LOF 또는 AIS 경보를 수신하거나 인터페이스가 작동하지 않습니다.

-

SSM이 DUS(Do-Not-Use) 상태이거나 SSM이 클럭의 품질이 낮음을 나타냅니다(즉, 참조의 SSM 품질이 TCC보다 낮음).

-

입력 주파수는 BITS의 경우 15ppm 이상, 30초 이상의 회선의 경우 16ppm 이상(범위 외)입니다.

-

입력 클럭이 불안정합니다. 즉, 시계가 2ppm을 초과하여 돌아다닌다는 의미입니다.

-

최소 30초 동안 검증되지 않았습니다.

단계 잠금 루프

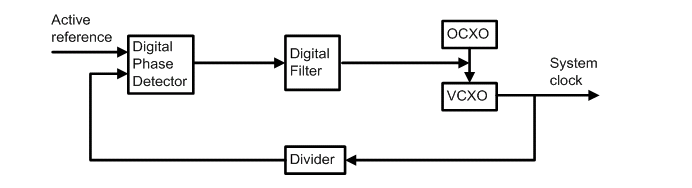

TCC의 타이밍 회로의 중심에는 PLL(phase-locked-loop)에 의해 생성된 클럭 생성기 블록이 있습니다. 그림 3은 TCC의 간소화된 PLL을 나타냅니다.

그림 3 - 단계 잠금 루프

위상 탐지기는 활성 참조 클럭을 시스템 클럭과 비교합니다(이미 분할선을 통해 분할됨). 위상 오프셋이 있으면 오프셋에 비례하는 전압 레벨이 생성됩니다.오프셋이 없으면 출력이 생성되지 않습니다.이 필터는 일정 기간 동안 전압 신호를 매끄거나 평균화하며, 평균을 VCXO(Voltage Controlled Crystal O진동)로 피드합니다. 전압은 VCXO의 위상과 빈도를 조정합니다.VCXO의 출력은 시스템 클럭(또는 NE 클럭)입니다. 출력의 일부가 루프로 다시 전달되어 프로세스를 반복합니다.시스템 클럭이 활성 참조를 추적하면 클럭이 잠기고 TCC가 일반 클럭 모드로 들어갑니다.

VCXO는 OCXO(오븐 제어 크리스탈 진동자)와 필터링된 참조 시계 사이의 더 작은 PLL로 안정됩니다.

참고: 다이어그램을 단순화하기 위해 이 작은 PLL은 여기에 표시되지 않습니다.

그 결과 시스템 시계가 더 안정적입니다.TCC에 사용된 OCXO는 Stratum 3에서 높은 안정성 및 무료 실행 정확성으로 평가됩니다.

카드 수준 동기화 지원

옵티컬 카드

-

시스템 클럭에는 모든 SONET 전송 인터페이스가 시간 표시됩니다.

-

포인터 조정을 사용하여 입력 시간과 출력 타이밍 간의 차이를 해결합니다.

DS1/DS3 카드

-

원래 DSx 입력 속도는 출력의 데이터 속도를 결정합니다.데이터 속도는 통과 타이밍 모드에 대한 NE 클럭과 완전히 독립적입니다.

-

SONET 네트워크의 초기 매핑 및 포인터 조정에서 NE 전송률과 데이터 전송률의 차이를 해결하려면 해당 비트를 사용합니다.

DS3XM 카드

-

출력 라인 속도가 NE 클럭에 잠겨 있습니다.

-

DS3 내의 개별 DS1은 입력 빈도를 유지합니다.

타이밍 모드

ONS 15454는 다음 타이밍 모드를 지원합니다.

-

외부

-

선

-

혼합

TCC 카드에는 Holdover 및 무료 실행 타이밍 지원을 제공하는 내부 Stratum 3 시계가 있습니다.

참고: 통과 타이밍 및 포트별 루프 타이밍은 추가 타이밍 모드입니다.그러나 ONS 15454 프로비저닝 플랫폼은 이러한 모드를 지원하지 않습니다.

참고: 전기 비동기 인터페이스는 시간이 초과되며 시스템 타이밍을 참조하지 않습니다.이러한 비동기 포트의 경우 전송 타이밍은 해당 비동기 신호에 대해 수신된 타이밍에서 파생됩니다.

외부 타이밍

이 모드는 BITS 또는 타이밍 DS-1/E1과 같은 외부 타이밍 장치에서 타이밍을 도출합니다. 외부 타이밍 장치의 품질 수준은 내부 Stratum 3 클럭보다 우수합니다.

라인 타이밍

라인 타이밍은 하나 이상의 옵티컬 인터페이스에서 타이밍 참조를 파생합니다.옵티컬 인터페이스가 여러 개인 옵티컬 카드는 타이밍 참조 포트로 하나의 인터페이스만 프로비저닝할 수 있습니다.수신 복구된 클럭은 19.44MHz 신호로 변환되고 TCC 카드로 전송되며 타이밍 참조로 적합합니다.라인 타이밍 모드에서 사용 가능한 타이밍 참조는 옵티컬 인터페이스와 내부 클럭입니다.

참고: 옵티컬 포트가 1+1로 프로비저닝되면 작업 포트만 타이밍 참조로 프로비저닝됩니다.보호 포트는 스위치 오버 중에 자동으로 선택됩니다.

혼합 타이밍

혼합 모드 타이밍을 통해 외부(BITS1/BITS2) 및 선(옵티컬 인터페이스) 타이밍 참조를 모두 선택하고 내부 클록을 선택할 수 있습니다.타이밍 루프가 쉽게 발생할 수 있으므로 혼합 모드 타이밍을 사용할 때는 주의해야 합니다.따라서 혼합 모드 타이밍을 사용하기 전에 신중하게 계획하십시오.또는 루프된 BITS를 사용합니다.

클럭 모드

일반 모드

일반 작업 모드에서는 TCC가 외부 타이밍 소스에 잠깁니다.

빠른 시작 모드

진동자는 발진기의 주파수와 거리가 먼 참조 시계의 빠른 '풀인'에 Fast-start 모드를 사용합니다.Fast-start는 'Acquire State'라고도 합니다.TCC가 TCC 카드가 이미 실행되는 속도에 가까운 참조로 변경되면 모드가 Normal로 직접 변경됩니다.

Holdover 모드

홀도버 모드에서는 모든 외부 또는 라인 타이밍 참조가 손실되고 클럭은 정상 작동 모드에서 참조된 타이밍 데이터를 사용하여 출력 신호를 제어합니다.그러나 시간 참조를 사용할 수 있을 때까지 대기 빈도는 시간이 지남에 따라 이동합니다.이전 타이밍 참조가 손실되기 140초 전에 사용 가능한 경우 타이밍 참조가 손실되면 TCC가 자유 실행 모드로 들어갑니다.

이 모드는 마지막 적격 타이밍 참조에서 얻은 평균 140초의 데이터를 사용하여 내부 클록을 증가시키기 때문에 자유 실행 모드보다 좋습니다.TCC는 스위치에 대한 참조를 사용할 수 있게 되거나 드리프트가 범위를 벗어날 때까지 이 모드로 유지됩니다.처음 24시간 동안 Holdover 모드로 전환하면 트래픽이 중단되지 않습니다.

자유 실행 모드

자유 실행 모드는 TCC 카드의 내부 클럭만 참조합니다.이 모드는 참조로 특별히 프로비저닝되지 않은 경우에도 다른 참조가 손실된 경우에도 기본 모드입니다.네트워크가 TCC 카드의 내부 시계와 함께 작동하지 않도록 유일한 또는 기본 타이밍 소스로 합니다.

동기화 계획 지침

적절한 타이밍 설계의 특징

적절한 타이밍 설계:

-

논리적 타이밍 계층을 통합합니다.

-

효율적인 동기화를 제공합니다.

-

타이밍 루프를 방지합니다.

-

타이밍 실패에서 신속하게 복구됩니다.

몇 개의 노드보다 큰 네트워크에 대해 이중화되고 정확한 외부 타이밍 소스를 갖는 것이 항상 가장 좋습니다.실제 네트워크에서는 이러한 작업이 항상 가능하거나 필요한 것은 아닙니다.

내부 타이밍은 정상 작동 중에 기본 타이밍 소스로 사용하기 위한 것이 아닙니다.Cisco에서는 다른 모든 타이밍 소스가 실패할 때 사용할 수 있는 내부 클럭과 함께 기본 네트워크 타이밍(기본 참조 소스/기본 참조 시계(PRS/PRC) 클럭)에 더 높은 품질의 소스를 사용하는 것이 좋습니다.

높은 추적이 가능하도록 마스터 노드의 데이지 체인 방식으로 시간 지정된 ONS 15454 노드 줄 수를 최소화합니다.일반적인 지침으로, 기본 방향에 최대 7개의 노드를, 보조 방향에 13개의 노드를 포함할 수 있습니다.타이밍 루프를 방지하기 위해 링에서 라인 타이밍을 신중하게 계획합니다.

타이밍 루프는 노드가 자체 클록을 추적하려고 할 때 큰 주파수 오류를 일으킬 수 있습니다. 그러면 ONS 15454 노드가 Holdover, Fast-start 또는 Free-run 타이밍 모드를 반복적으로 입력할 수 있습니다.타이밍 루프가 있음을 나타내는 경보가 없는 경우가 많습니다.

관련 정보

개정 이력

| 개정 | 게시 날짜 | 의견 |

|---|---|---|

1.0 |

01-Jan-2006

|

최초 릴리스 |

피드백

피드백