Cisco 7200 Parity Error Fault Tree

Sommario

Introduzione

In questo documento viene descritto come risolvere i problemi e isolare la parte o il componente di un Cisco 7200 che ha esito negativo quando si identificano vari messaggi di errore di parità. Si consiglia di leggere Risoluzione dei problemi di blocco del router e degli errori di parità della memoria del processore (PMPE) prima di procedere con questo documento.

Nota: le informazioni di questo documento si basano sui router Cisco serie 7200.

Prerequisiti

Requisiti

Non sono previsti prerequisiti specifici per questo documento.

Componenti usati

Il documento può essere consultato per tutte le versioni software o hardware.

Le informazioni discusse in questo documento fanno riferimento a dispositivi usati in uno specifico ambiente di emulazione. Su tutti i dispositivi menzionati nel documento la configurazione è stata ripristinata ai valori predefiniti. Se la rete è operativa, valutare attentamente eventuali conseguenze derivanti dall'uso dei comandi.

Convenzioni

Per ulteriori informazioni sulle convenzioni usate, consultare il documento Cisco sulle convenzioni nei suggerimenti tecnici.

Analisi struttura errori parità NPE (Network Processing Engine)

In questo diagramma viene descritto come determinare quale parte o componente di Cisco 7200 ha esito negativo quando si identificano diversi messaggi di errore di parità.

Nota: acquisire e registrare l'output show tech-support e i log della console e raccogliere tutti i file crashinfo durante gli eventi di errore di parità.

Rilevamento errori di parità NPE e messaggi

Questa sezione contiene diagrammi a blocchi di NPE e in cui questi sistemi rilevano errori di parità. Di seguito è disponibile una descrizione di ciascun tipo di messaggio di errore.

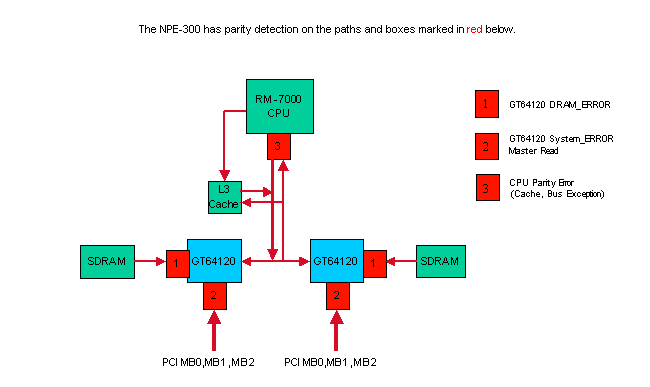

Errori di parità in NPE-300

NPE-300 utilizza il controllo della parità nella memoria condivisa (SDRAM), il bus PCI e l'interfaccia esterna della CPU per proteggere il sistema da errori di bit. Il controllo della parità è in grado di rilevare un errore su un singolo bit utilizzando un metodo semplice; aggiunta di un bit di controllo per otto bit di dati. Se viene rilevato un errore di bit durante il passaggio dei dati tra i componenti hardware, il sistema elimina i dati errati. Gli errori di bit singolo in qualsiasi punto del diagramma precedente causano il reset del router.

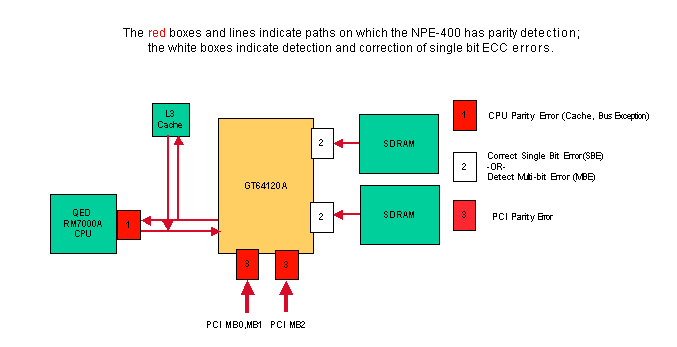

Rilevamento parità/ECC NPE-400

NPE-400 utilizza le funzioni Single Bit Error Correction (correzione degli errori a bit singolo) e Multi-Bit Error Detection ECC (correzione del codice di errore) per la memoria condivisa (SDRAM). Per aumentare la disponibilità del sistema in NPE-400, ECC corregge gli errori di bit singolo nella SDRAM, per consentire al sistema di funzionare normalmente senza reimpostare e senza tempi di inattività. Per ulteriori informazioni su come ECC migliora la disponibilità del sistema, consultare la pagina Incremento della disponibilità della rete.

Un errore a più bit nella SDRAM causa il reset del router con un errore della cache o del bus. Il resto della memoria e dei bus nel sistema usano il rilevamento della parità a bit singolo. Gli errori di bit singolo a 1 e 3 nel diagramma precedente causano il reset del router.

Errori di parità nel router C7200

Diversi dispositivi di controllo della parità sul router C7200/NPE possono segnalare dati con parità non valida per qualsiasi operazione di lettura o scrittura. Di seguito è riportata una descrizione dei vari messaggi di errore riportati su un sistema C7200/NPE:

Errore DRAM GT64010/GT64120

Questo errore viene segnalato quando un controller di sistema GT64120 rileva un errore di parità durante la lettura di SDRAM:

%ERR-1GT64120 (PCI0):Fatal error, Memory parity error (external) GT=0xB4000000, cause=0x0100E283, mask=0x0ED01F00, real_cause=0x00000200 Bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x1C000000

Sostituire la SDRAM dopo un secondo errore. Se il problema persiste, sostituire NPE.

Nota: Per gli NPE meno recenti (NPE-100/150/2000) che utilizzano i controller GT64010, l'errore è simile al seguente:

%ERR-1-GT64010: Fatal error, Memory parity error (external) cause=0x0300E283, mask=0x0CD01F00, real_cause=0x00000200 bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x00000000

Il controller GT64010 utilizza la RAM dinamica (DRAM) e non la SDRAM. In questo caso, sostituire la DRAM dopo un secondo guasto. Se il problema persiste, sostituire NPE.

GT64010/GT64120 - Lettura master errori di parità sistema

Un errore di parità in lettura master è un errore di parità generato dall'accesso a un bridge PCI (Peripheral Component Interconnect). Di seguito è riportato un esempio di output dell'errore di parità:

%ERR-1-GT64120 (PCI0):Fatal error, Parity error on master read GT=B4000000, cause=0x0110E083, mask=0x0ED01F00, real_cause=0x00100000 Bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x00000470 %ERR-1-SERR: PCI bus system/parity error %ERR-1-FATAL: Fatal error interrupt, No reloading Err_stat=0x81, err_enable=0xFF, mgmt_event=0x40

Sostituite il componente appropriato dopo un secondo fallimento. Il dump del bridge di sistema indica il componente da sostituire.

System bridge dump:

Bridge 1, for PA bay 1, 3 and 5. Handle=1

DEC21150 bridge chip, config=0x0

(0x1C):sec status, io base =0x83A09141

Detected Parity Error on secondary bus

Data Parity Detected on secondary bus

(0x20):mem base & limit =0x4AF04880

Queste tabelle indicano quale componente presenta un possibile problema dall'output del messaggio di errore.

NPE-100/150/2010:

| Numero bridge | A cosa serve il ponte | Errore di parità sul bus primario | Errore di parità sul bus secondario |

|---|---|---|---|

| Ponte 0 | Downstream da MB0 a MB1.0 | Sostituire NPE | Sostituire NPE; se ancora presente, sostituire lo chassis |

| Ponte 1 | Upstream da MB1 a MB0 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire NPE |

| Ponte 2 | Downstream da MB0 a MB2 | Sostituire NPE | Sostituire NPE; se ancora presente, sostituire lo chassis |

| Ponte 3 | Upstream da MB2 a MB0 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire NPE |

NPE-175/225/300/400/NSE-1:

| Numero bridge | A cosa serve il ponte | Errore di parità sul bus primario | Errore di parità sul bus secondario |

|---|---|---|---|

| Ponte 0 | Per alloggiamento PA 0 (scheda I/O, PCMCIA, interfacce | Sostituire NPE | Sostituire NPE; se ancora presente, sostituire la scheda I/O. Se ancora presente, sostituire lo chassis |

| Ponte 1 | Per l'alloggiamento PA 1, 3 e 5 | Sostituire NPE | Sostituire l'NPE; se ancora presente, sostituire lo chassis |

| Ponte 2 | Per l'alloggiamento PA 2, 4 e 6 | Sostituire NPE | Sostituire NPE; se ancora presente, sostituire lo chassis |

Tutti i modelli C7200:

| Numero bridge | A cosa serve il ponte | Errore di parità sul bus primario | Errore di parità sul bus secondario |

|---|---|---|---|

| Ponte 4 | Port Adapter 1 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire PA 1; se ancora presente, sostituire lo chassis |

| Ponte 5 | Port Adapter 2 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire PA 2; se ancora presente, sostituire lo chassis |

| Ponte 6 | Port Adapter 3 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire PA 3; se ancora presente, sostituire lo chassis |

| Ponte 7 | Port Adapter 4 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire PA 4; se ancora presente, sostituire lo chassis |

| Ponte 8 | Port Adapter 5 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire PA 5; se ancora presente, sostituire lo chassis |

| Ponte 9 | Port Adapter 6 | Sostituire NPE; se ancora presente, sostituire lo chassis | Sostituire PA 6; se ancora presente, sostituire lo chassis |

Errore di parità CPU

Come per tutti i computer e i dispositivi di rete, l'NPE è soggetta alla rara presenza di errori di parità nella memoria del processore. Gli errori di parità possono causare il reset del sistema e possono essere un singolo evento di disturbo temporaneo (SEU o errore software) o possono verificarsi più volte (spesso definiti errori hardware) a causa di hardware danneggiato. Per ulteriori informazioni sulle SEU, consultare la pagina Aumento della disponibilità della rete. Un errore di parità della CPU viene segnalato se la CPU rileva un errore di parità quando accede a una qualsiasi cache del processore (L1, L2 o, se presente, L3).

Di seguito sono riportati quattro esempi di questo tipo di errore:

Esempio 1:

Error: SysAD, data cache, fields: data, 1st dword

Physical addr(21:3) 0x195BE88,

Virtual address is imprecise.

Imprecise Data Parity Error

Imprecise Data Parity Error

NPE dispone di un processore R7K con cache non bloccante. Per cache non bloccante si intende quando esegue un'istruzione per caricare dati in un registro e questi dati non si trovano nella cache L1, la CPU carica i dati da una cache di ordine inferiore o dai dati SDRAM. La CPU non blocca l'esecuzione di ulteriori istruzioni a meno che non si verifichi un altro errore nella cache o un'altra istruzione dipenda dai dati caricati. Ciò consente di velocizzare notevolmente il processore e di migliorare le prestazioni, ma può anche causare errori di parità imprecisi. Un errore di parità impreciso si verifica quando la CPU legge le informazioni senza bloccarle e successivamente determina che si è verificato un errore di parità nella riga della cache associata. Il processore R7K non è in grado di dirci esattamente quale istruzione era in esecuzione durante il caricamento della linea della cache, e questo è il motivo per cui lo chiamiamo errore di parità impreciso.

Anche se i sistemi utilizzano ECC (Error Code Correction), è comunque possibile visualizzare un errore di parità occasionale quando si sono verificati più errori nei 64 bit di dati a causa di un errore nella cache.

Un errore di parità si verifica quando un valore di bit del segnale viene modificato dal valore originale (0 o 1) al valore opposto. Questo errore può verificarsi a causa di un errore di parità soft o hard.

Gli errori di parità soft si verificano a causa di un'influenza esterna sulla memoria del dispositivo, che modifica il valore di bit al livello corrente. Questo tipo di problema è transitorio e non si verifica di nuovo. Gli errori di parità hardware si verificano quando il valore di bit viene modificato dalla memoria stessa a causa di un danno alla memoria. In questo caso, il problema si verifica ogni volta che viene utilizzata quell'area di memoria, il che significa che il problema può ripetersi più volte in un paio di giorni a una settimana.

Esempio 2:

Error: SysAD, instr cache, fields: data, 1st dword

Physical addr(21:3) 0x000000,

virtual addr 0x6040BF60, vAddr(14:12) 0x3000

virtual address corresponds to main:text, cache word 0

Low Data High Data Par Low Data High Data Par

L1 Data: 0:0xAE620068 0x8C830000 0x00 1:0x50400001 0xAC600004 0x01

2:0xAC800000 0x00000000 0x02 3:0x1600000B 0x00000000 0x01

Low Data High Data Par Low Data High Data Par

DRAM Data: 0:0xAE620068 0x8C830000 0x00 1:0x50400001 0xAC600004 0x01

2:0xAC800000 0x00000000 0x02 3:0x1600000B 0x00000000 0x01

Esempio 3:

Cache Err Reg = 0xE4588D10 Data reference, Secondary/Sys intf cache, Data field error Error on 1st doubleword on System interface No errors in addition to instr error Data phy addr that caused last parity or bus error: 0x1E84040C

Esempio 4 (solo NPE-300 e NPE-400):

%CERF-3-RECOVER: PC=0x604F136C, Origin=L3 Data ,PhysAddr=0x013CEFD0

o

%SYS-2-CERF_ABORT: Reason=0xEE23, PC=0x604629C8, Origin=L3 Data, Phys Addr=0x0287A4E8

Entrambi i messaggi riportati sopra sono accompagnati da un report relativo alla funzione di recupero degli errori della cache (CERF, Cache Error Recovery Function), come indicato di seguito:

CERFa[1 ] 05:25:36 MET Tue Jul 9 2002: result=0xEE23; instr_pos=-2; rpl_off=1 CERFb[1 ] PC =604629C8; ORGN=L3 Data; PRID=00002710; PHYA=0287A4E8 CERFc[1 ] SREG=3400E105; CAUS=00000400; DEA0=0287A4E8; ECC =00000000 CERFd[1 ] CERR=E447A4EA; EPC =606361F8; DEA1=02517058; INFO=00000000 CERFe[1 ] CACHE=28FF78B4 62B36D98 02020684 00000E17 00000030 00000001 61F2934C 3EDA025D CERFe[1 ] SDRAM=28FF78B4 62B36D98 02020684 00000E17 00000030 00000001 61F2934C 3EDA025D CERFg[1 ] CXT =00000000; XCXT=00000000; BVAD=00000008; PFCL=00000000 CERFh[1 ] ISeq: 0045182B; 1060000E; 2C4203E9; 92430028; 38420001; 30630005 CERFi[1 ] o0 $3 ....; beq....; sltiu $2 ....; lbu $3, 0x0028($18); xori $2....; andi $3 ....;* CERFj[1 ] ; ; ; 6287A4E8; ; ; CERFk[1 ] ResumptionCode= 0x92430028; 0x0000000F; 0x42000018 CERFl[1 ] Instr's checked=4; diags=0x00000158,0x00040000,3600,1,0 CERFm[1 ] BaseRegLost later/off: 0/0 times; StoredValueLost: 0 times CERFn[1 ] INFO=00000000; CNFG=5061F4BB; ICTL=00000000 Initial Register Values CERFs00[1 ] $0=00000000 AT=61A30000 v0=00000001 v1=00000002 CERFs04[1 ] a0=28FF8728 a1=00003A98 a2=00000000 a3=00000007 CERFs08[1 ] t0=00000000 t1=3400E101 t2=606381E0 t3=FFFF00FF CERFs12[1 ] t4=606381C8 t5=000005D4 t6=00000008 t7=61C50000 CERFs16[1 ] s0=6189C188 s1=00000000 s2=6287A4C0 s3=00003A98 CERFs20[1 ] s4=61BD57B0 s5=00000006 s6=00000000 s7=61BD6C60 CERFs24[1 ] t8=60634788 t9=00000000 k0=621A8374 k1=6063EA40 CERFs28[1 ] gp=61A33B20 sp=61E28678 s8=00000000 ra=60462CA4 1 Cache error exceptions already reported

Se CERF è abilitato su NPE-300 o NPE-400 e si verifica un errore di parità, verranno visualizzati i registri sopra riportati. Per ulteriori informazioni su CERF, fare riferimento alla sezione Soluzioni riportata di seguito.

Soluzioni

Quando si verificano tali errori, si consiglia di procedere come segue:

-

Monitorare l'hardware interessato per verificare se lo stesso problema si verifica di nuovo. In caso contrario, si è trattato di un problema temporaneo di tipo Single Event Upset (SEU) e non è necessario eseguire alcuna azione.

-

Nell'improbabile eventualità che il problema si ripresenti, il comando cache L3 bypass/disable è un'opzione che può aiutare a ridurre l'impatto del problema. Questo comando è disponibile solo sulle seguenti piattaforme:

-

7200 con processore NPE-300, NPE-400 o NSE-1

-

7400 con processore engine NSE-1

Poiché NPE-300 non supporta la memoria ECC, questa funzione è particolarmente importante per aumentare la disponibilità del sistema e gestire questi errori di parità senza interrompere il servizio. In questo modo vengono risolti molti errori di parità soft. L'avvertenza è che si verifica un leggero impatto sulle prestazioni del sistema quando la cache L3 è disabilitata. Il peggioramento delle prestazioni è compreso tra l'1% e il 10% a seconda della configurazione del sistema. La sintassi per l'utilizzo di questo comando dipende dalla versione del software Cisco IOS.

-

Il comando cache L3 disable è disponibile a partire da Cisco IOS versione 12.3(5a). Sarà disponibile anche nella versione 12.1(22)E. In queste versioni, la cache L3 è disabilitata per impostazione predefinita, pertanto non è necessaria alcuna azione per sfruttare questa funzione. La cache L3 può essere riattivata con il comando no cache L3 disable.

-

Il comando cache L3 bypass è disponibile nelle versioni software Cisco IOS 12.2(6)S, 12.2(6)B, 12.2(8)BC1b, 12.0(20)SP, 12.2(6)PB, 12.2(2)DD2, 12.0(20)ST3, 12.0(21)S, 12.1(11)EC, 12.2(7)T, 12.1(13), 12.2(7) o versioni successive e da 12.1(11)E a 12.1(21)E. Questo comando è disabilitato per impostazione predefinita.

Per abilitare il bypass della cache L3, immettere quanto segue dalla modalità di configurazione:

Router(config)#cache L3 bypass

Per disabilitare il bypass della cache L3, immettere quanto segue dalla modalità di configurazione:

Router(config)#no cache L3 bypass

La nuova impostazione della cache non ha effetto finché il router non viene ricaricato.

All'avvio del router, vengono visualizzate le informazioni di sistema, incluse quelle sulla cache L3. Infatti il file startup-config non è ancora stato elaborato dal sistema. Dopo l'elaborazione del file di configurazione di avvio, la cache L3 viene ignorata se il comando cache L3 bypass si trova nella configurazione.

Per verificare l'impostazione della cache L3, è possibile usare il comando show version. Se la cache L3 viene ignorata, nell'output show version non è presente alcun riferimento alla cache L3.

-

-

Un'altra funzionalità che contribuisce ad aumentare la disponibilità del sistema è la funzione di recupero da errori della cache (CERF, Cache Error Recovery Function). Quando questa funzione è attivata (questa è l'impostazione predefinita nelle ultime versioni del software Cisco IOS, ma a partire da febbraio 2004, solo per NPE-300 e NPE-400), il software Cisco IOS tenta di risolvere l'errore di parità e di evitare il crash del processore. Questa funzione risolve circa il 75% di alcuni tipi di errori di parità soft. Richiamando questo comando, il sistema rileva una riduzione delle prestazioni inferiore al 5%.

Il file CERF per NPE-300 è disponibile nei software Cisco IOS versione 12.1(15), 12.1(12)EC, 12.0(22)S, 12.2(10)S, 12.2(10)T, 12.2(10), 12.2(2)XB4, 12.2(11)BC1b e 12.1(5)XM8 o successive.

CERF per NPE-400 può essere trovato in 12.3(3)B, 12.2(14)S3, 12.1(20)E, 12.1(19)E1, 12.3(1a), 12.2(13)T5, 12.2(18)S, 12.3(2)T, 12.2(18), 12.3(3), e 12.3(1)B1 o successive.

Il modulo CERF per NPE-300 richiede la revisione hardware 4.1 o successiva. Per identificare la versione hardware di NPE-300, utilizzare il comando show c7200.

Router>show c7200 ... C7206VXR CPU EEPROM: Hardware revision 4.1 Board revision A0 ...

Il CERF per NPE-400 richiede il processore R7K revisione 2.1 o superiore. Per identificare la revisione del processore dell'NPE-400, utilizzare il comando show version.

Router>show version ... cisco 7206VXR (NPE400) processor with 491520K/32768K bytes of memory. R7000 CPU at 350Mhz, Implementation 39, Rev 3.2, 256KB L2, 4096KB L3 Cache 6 slot VXR midplane, Version 2.1 ...

Nota: è importante raccogliere tutti i file crashinfo rilevanti per determinare la causa principale dell'errore, come spiegato in Recupero delle informazioni dal file Crashinfo.

Se i suggerimenti sopra riportati non risolvono il problema, la sostituzione dell'NPE può essere utile in caso di ripetuti errori di parità, poiché gli errori di parità hardware sono dovuti a hardware danneggiato. Le sostituzioni hardware sono identiche all'NPE originale. La sostituzione di NPE non garantisce che non si verificheranno ulteriori errori di parità poiché i Single Event Upset (SEU) sono inerenti a qualsiasi computer dotato di memoria.

Informazioni correlate

Cronologia delle revisioni

| Revisione | Data di pubblicazione | Commenti |

|---|---|---|

1.0 |

13-Apr-2009 |

Versione iniziale |

Feedback

Feedback