# Power and I/O Signals at the ESR BTB Connector

This chapter contains the following sections:

- Power and I/O Signals at the ESR BTB Connector, on page 1

- Power Signals, on page 1

- LED Control Signals, on page 3

- Gigabit Ethernet Port Signals, on page 5

- Module Interface Signals, on page 7

- External Port Signals, on page 8

- Miscellaneous Control Signals, on page 10

### Power and I/O Signals at the ESR BTB Connector

This section contains tables describing the control signals for different components. In the following tables, you will see the terms PU and PD. These stand for:

- PU = Pull-Up resistor

- PD = Pull-Down resistor

Note

Differential pairs should be mostly routed on inner layers where the impedance tolerance is controlled better. Outer layers should only be used for very short differential pair traces (less than 0.25").

### **Power Signals**

| Signal Name | Direction | Terminations                                            | Description                                | Levels  |

|-------------|-----------|---------------------------------------------------------|--------------------------------------------|---------|

| +5V         | IN        | _                                                       | +5V Power Input to ESR board               | 5V DC   |

| +3.3V       | IN        | —                                                       | +3.3V Power Input to ESR board             | 3.3V DC |

| RTC_3.0V    | IN        | Series 1K resistor<br>required at Host<br><b>Note 6</b> | +3.0V RTC Battery Power Input to ESR board | 3.0V DC |

| Signal Name          | Direction | Terminations            | Description                                                                                                                                                                                                                                                                                                                    | Levels  |

|----------------------|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| GND                  | —         |                         | Ground                                                                                                                                                                                                                                                                                                                         | GND     |

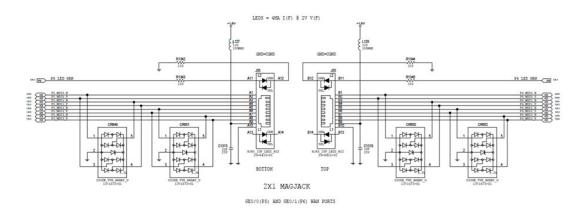

| +1.8V_OUT            | OUT       |                         | <ul> <li>+1.8V output from ESR board</li> <li>Caution         <ol> <li>1.8V source is only intended for use as a WAN port center tap voltage as shown in the reference design schematic. 50mA is the max that can be drawn from that 1.8V output.</li> </ol> </li> <li>See EVK Schematics below for further detail.</li> </ul> | 1.8V DC |

| P3V3_TRIM            |           |                         | Trim signal to margin 3.3V +/-5%       Passiv         See reference design schematic for proper usage.       (For test purposes only. Leave unconnected if not used.)                                                                                                                                                          |         |

| DCIN_PWR_GOOD Note 8 | IN        | 50K PU at ESR<br>Note 1 | <ul> <li>External Power Supply Status Detect input (3.3V digital signal at the ESR connector).</li> <li>Can be used as an early power failure detect of the main power source.</li> <li>Active High (0 = Power Supply status is not good. 1 = Power Supply status is good.)</li> </ul>                                         |         |

**Note 1**: Signal driver can be open drain with a strong pullup (4.7K to 10K), or can be driven by 3.3V push-pull levels. A pull-down is not allowed on this signal. Can be left unconnected if not used.

Note 6: Series 1K current-limiting resistor is required on the host board for the RTC 3.0V battery.

**Note 8**: (currently not supported by software for graceful shutdown, but could be in the future). Used for successful CPU power up and boot. Must be driven or pulled high at powerup, or left open (because it is already pulled up by the ESR and keeps it in a "good" state for proper power up and CPU boot if left open).

#### Figure 1: EVK Schematic

## **LED Control Signals**

| Signal Name   | Direction | Terminations                     | Description                                                                                                                                     | Levels    |

|---------------|-----------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| SYS_LED_GRN_L | OUT       | 10K PD at ESR                    | System Green LED Enable (active low)                                                                                                            | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at       |                                                                                                                                                 |           |

|               |           | Host.                            |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| SYS_LED_YEL_L | OUT       | 10K PD at ESR                    | System Yellow LED Enable (active low)                                                                                                           | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| ALM_LED_RED   | OUT       | 1K PD at ESR                     | Alarm Red LED Enable (active high)                                                                                                              | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| VPN_LED_GRN   | OUT       | 4.7K PU at ESR                   | VPN Green LED Enable (active high)                                                                                                              | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| R0_LED        | OUT       | 270 Ohm series resistor at       | Row 0 LED control for LAN Ports GE 1/1 and GE 1/0.                                                                                              | 3.3V CMOS |

|               |           | Host.                            | (controls cathode-side of 2 single-color LEDs).                                                                                                 |           |

|               |           | Note 7                           | Cathode-side LED Enable (driven by Ethernet Switch on ESR) - Active Low.                                                                        |           |

|               |           |                                  | Tie to Cathode side of two single-color Green LEDs through a resistor to each (e.g., 270 ohms for a 5mA forward current on each of the 2 LEDs). |           |

| Signal Name  | Direction | Terminations                        | Description                                                                                                                                            | Levels    |

|--------------|-----------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| C0_LED       | OUT       | 4.7K PD at ESR<br>Note 3            | Column 0 LED control for LAN Ports GE 1/2 and GE 1/0.                                                                                                  | 3.3V CMOS |

|              |           |                                     | (controls anode-side of 2 single-color LEDs).                                                                                                          |           |

|              |           |                                     | (Anode-side LED Enable (driven by Ethernet Switch on ESR) - Active high.                                                                               |           |

|              |           |                                     | Tie <b>DIRECTLY</b> to Anode side of two single-color Green LEDs.                                                                                      |           |

| R1_LED       | OUT       | 270 Ohm series resistor at<br>Host. | Row 1 LED control for LAN Ports <b>GE 1/3</b> and <b>GE 1/2</b> .                                                                                      | 3.3V CMOS |

|              |           | Note 7                              | (controls cathode-side of 2 single-color LEDs).                                                                                                        |           |

|              |           |                                     | Cathode-side LED Enable (driven by Ethernet Switch on ESR) - Active Low.                                                                               |           |

|              |           |                                     | Tie to Cathode side of two single-color Green LEDs through a resistor to each (for example, 270 ohms for a 5mA forward current on each of the 2 LEDs). |           |

| C1_LED       | OUT       | 4.7K PD at ESR<br>Note 3            | Column 1 LED control for LAN Ports <b>GE 1/3</b> and <b>GE 1/1</b> .                                                                                   | 3.3V CMOS |

|              |           |                                     | (controls anode-side of 2 single-color LEDs).                                                                                                          |           |

|              |           |                                     | (Anode-side LED Enable (driven by Ethernet Switch on ESR) - Active high.                                                                               |           |

|              |           |                                     | Tie <b>DIRECTLY</b> to Anode side of two single-color Green LEDs.                                                                                      |           |

| P5_LED_GRN   | OUT       | 270 Ohm series resistor at Host.    | WAN Copper Port (GE 0/0) LED Enable (controlled by Ethernet PHY on ESR) - Active High                                                                  | 3.3V CMOS |

|              |           | Note 7                              |                                                                                                                                                        |           |

| SFP1_LED_YEL | OUT       | 270 Ohm series resistor at<br>Host. | WAN SFP Port (SFP 0/0) LED Enable (controlled by<br>Ethernet PHY on ESR) - Active High                                                                 | 3.3V CMOS |

|              |           | Note 7                              |                                                                                                                                                        |           |

| P6_LED_GRN   | OUT       | 270 Ohm series resistor at<br>Host. | WAN Copper Port (GE 0/1) LED Enable (controlled<br>by Ethernet PHY on ESR) - Active High                                                               | 3.3V CMOS |

|              |           | Note 7                              |                                                                                                                                                        |           |

| SFP2_LED_YEL | OUT       | 270 Ohm series resistor at<br>Host. | WAN SFP Port (SFP 0/1) LED Enable (controlled by<br>Ethernet PHY on ESR) - Active High                                                                 | 3.3V CMOS |

|              |           | Note 7                              |                                                                                                                                                        |           |

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration

of the ESR CPU and should not be changed, as they are necessary during system reset to configure bootup settings. However, after any system reset (after system boots up), those signals are free to be driven and free to change states.

**Note 7**: Series current-limiting resistor is required on host board for the LED driving signals. LEDs on host board should be chosen so that they operate well at 5mA forward current.

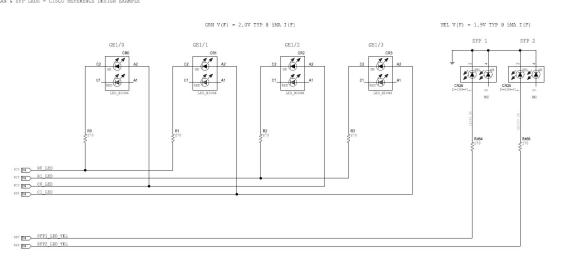

See the following figure for a design reference.

#### Figure 2: LAN and SFP LED Reference Design

NOTES FOR INTEGRATORS

Note

The Marvell Ethernet PHY chip set controls the LEDs, simply implement as shown in the reference design schematics. The Marvell chip minimizes the number of control lines by row and column to convey the correct link state and activity indication for all 4 ports. Cisco software does not control the ethernet port LEDs directly.

### **Gigabit Ethernet Port Signals**

| Signal Name       | Direction | Terminations                    | Description                                            | Levels        | Impedance                                                             |

|-------------------|-----------|---------------------------------|--------------------------------------------------------|---------------|-----------------------------------------------------------------------|

| SFP_2_TXD_[ P/N ] | OUT       | Series Caps at<br>SFP<br>Note 2 | Port 6 (WAN SFP 0/1) SFP Transmit<br>Differential Pair | 1.6V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_2_RXD_[ P/N ] | IN        | Series Caps at<br>SFP<br>Note 2 | Port 6 (WAN SFP 0/1) SFP Receive<br>Differential Pair  | 2.1V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| Signal Name           | Direction | Terminations                           | Description                                                                                    | Levels        | Impedance                                                             |

|-----------------------|-----------|----------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------|

| SFP_1_TXD_[ P/N ]     | OUT       | Series Caps at<br>SFP<br><b>Note 2</b> | Port 5 (WAN SFP 0/0) SFP Transmit<br>Differential Pair                                         | 1.6V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_1_RXD_[P/N]       | IN        | Series Caps at<br>SFP<br><b>Note 2</b> | Port 5 (WAN SFP 0/0) SFP Receive<br>Differential Pair                                          | 2.1V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P6_MDI[30]_[ P/N<br>] | BI        |                                        | Port 6 (WAN GE 0/1) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 2.8V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P5_MDI[30]_[ P/N<br>] | BI        |                                        | Port 5 (WAN GE 0/0) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 2.8V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P4_MDI[30]_[ P/N<br>] | BI        | _                                      | Port 4 (LAN GE 1/3) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P3_MDI[30]_[ P/N<br>] | BI        |                                        | Port 3 (LAN GE 1/2) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P2_MDI[30]_[ P/N<br>] | BI        | _                                      | Port 2 (LAN GE 1/1) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P1_MDI[30]_[ P/N<br>] | BI        | _                                      | Port 1 (LAN GE 1/0) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

# **Module Interface Signals**

| Signal Name              | Direction | Terminations                                                                                                  | Description                                                                       | Levels           | Impedance                                                            |

|--------------------------|-----------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| PCIE_REFCLK_[<br>P/N ]   | OUT       | If not used, keep open.<br>The router will disable<br>the PCIE reference<br>clock when no PCIe is<br>present. | PCIe 100MHz Differential Pair<br>Reference Clock for Pluggable<br>or SSD Module   | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_SGMII_TX_[<br>P/N ]  | OUT       | Series Caps at PIM<br>Note 2                                                                                  | SGMII Transmit Differential Pair<br>for Pluggable Module (Can be<br>PCIe TX also) | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_SGMII_RX_[<br>P/N ]  | IN        | Series Caps at ESR<br>Note 2                                                                                  | SGMII Receive Differential Pair<br>for Pluggable Module (Can be<br>PCIe RX also)  | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_USB3_TX_[<br>P/N ]   | OUT       | Series Caps at ESR<br>Note 2                                                                                  | USB 3.0 Transmit Differential<br>Pair for Pluggable Module                        | 1.2V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_USB3_RX_[<br>P/N ]   | IN        | Series Caps at PIM<br>Note 2                                                                                  | USB 3.0 Receive Differential<br>Pair for Pluggable Module                         | 1.2V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_USB2_[<br>DP/DN ]    | BI        | 2x 15K PD at ESR                                                                                              | USB 2.0 Differential Pair for<br>Pluggable Module                                 | 3.6V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_UA2_TXD              | OUT       | 10K PU at PIM<br>Note 3                                                                                       | UART2 Transmit Data for<br>Pluggable Module                                       | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_UA2_RXD              | IN        | 4.7K PU at ESR<br>Note 3                                                                                      | UART2 Receive Data for<br>Pluggable Module                                        | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| SSD_TX_SERDES_[<br>P/N ] | OUT       | Series Caps at Host<br>Note 4                                                                                 | SERDES Transmit Differential<br>Pair for SSD Module (Can be<br>SATA or PCIe)      | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| Signal Name              | Direction | Terminations                                                                                                             | Description                                                                                                                      | Levels           | Impedance                                                            |

|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| SSD_RX_SERDES_[<br>P/N ] | IN        | Series Caps at ESR<br>Note 2                                                                                             | SERDES Receive Differential<br>Pair for SSD Module (Can be<br>SATA or PCIe)                                                      | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_PWR_EN               | OUT       | 1K PD at PIM<br>Note 3                                                                                                   | Power Enable signal for the<br>Pluggable Module.<br>Active high (0 = disable<br>Pluggable power. 1 = Enable<br>Pluggable power.) | 3.3V CMOS        |                                                                      |

| PIM_GPS                  | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | GPS Pulse Per Second Timing<br>signal from Pluggable Module                                                                      | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.

Note 4: Series caps required on the host board for these SERDES signals.

### **External Port Signals**

| Signal Name         | Direction | Terminations                  | Description                                                      | Levels          | Impedance                                                           |

|---------------------|-----------|-------------------------------|------------------------------------------------------------------|-----------------|---------------------------------------------------------------------|

| USB3A_TX_[<br>P/N ] | OUT       | Series Caps at ESR<br>Note 2  | USB 3.0 Transmit Differential Pair<br>for External USB Host Port | 1.2V Max<br>USB | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| USB3A_RX_[<br>P/N ] | IN        | Series Caps at Host<br>Note 4 | USB 3.0 Receive Differential Pair<br>for External USB Host Port  | 1.2V Max<br>USB | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| USBA_[ DP/DN<br>]   | BI        | 2x 15K PD at ESR              | USB 2.0 Differential Pair for<br>External USB Host Port          | 3.6V Max<br>USB | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| Signal Name | Direction | Terminations                    | Description                                                                                                                                        | Levels    | Impedance                                                            |

|-------------|-----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------|

| USBA_5V_EN  | OUT       | 1K PD at ESR<br>Note 3          | Enable 5V output of the external<br>USB Host Port.<br>Active High (0 = disable 5V USB<br>output. 1 = enable USB 5V output)                         | 3.3V CMOS |                                                                      |

| USBA_OC_L   | IN        | 10K PU at Host<br>Note 5        | Over Current Detect of the external<br>USB Host Port.<br>Active Low (0 = USB host port 5V<br>is in overcurrent condition. 1 =<br>Normal Operation) | 3.3V CMOS |                                                                      |

| CP_UA0_DTR  | OUT       | 10K PU at Host<br>Note 5        | UART0 DTR flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_DSR  | IN        | 4.7K PU at ESR<br><b>Note 3</b> | UART0 DSR flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_RTS  | OUT       | 10K PU at Host<br>Note 5        | UART0 RTS flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_CTS  | IN        | 4.7K PU at ESR<br>Note 3        | UART0 CTS flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_TXD  | OUT       | 10K PU at Host<br>Note 5        | UART0 Transmit Data for external<br>RS232 Serial Port                                                                                              | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_RXD  | IN        | 4.7K PU at ESR<br>Note 3        | UART0 Receive Data for external<br>RS232 Serial Port                                                                                               | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| AP_UA0_TXD  | OUT       | 1K PD at ESR<br>Note 3          | Transmit Data for Console Port                                                                                                                     | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| AP_UA0_RXD  | IN        | 100K PU at Host<br>Note 5       | Receive Data for Console Port                                                                                                                      | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| Signal Name  | Direction | Terminations                                                                                                             | Description                                                                                                                                                 | Levels    | Impedance |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|

| ALM_IN_L     | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | Alarm Input (3.3V digital signal at<br>the ESR connector).<br>Active Low (0 = external alarm port<br>is closed. 1 = external alarm port is<br>open circuit) | 3.3V CMOS |           |

| PUSHBUTTON_L | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | Pushbutton Detect Input (3.3V<br>digital signal at the ESR connector).<br>Active Low (0 = pushbutton is<br>closed. 1 = pushbutton is open).                 | 3.3V CMOS |           |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.

Note 4: Series caps required on the host board for these SERDES signals.

Note 5: PU/PD are required on the host board for these signals.

## **Miscellaneous Control Signals**

| Signal Name | Direction | Terminations                       | Description                                                                                                                                                                                                                                      | Levels       | Impedance                                                            |

|-------------|-----------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------|

| EVK_INT_L   | IN        | 4.7K PU at<br>ESR<br><b>Note 3</b> | Reserved for Interrupt input to the ESR CPU from<br>the host board. Currently not used by the Cisco<br>Software to detect interrupts from the host<br>motherboard. User should leave this signal<br>unconnected, as the ESR provides the pullup. | 3.3V<br>CMOS |                                                                      |

| I2C2_SCL    | OUT       | 4.7K PU at<br>ESR<br>Note 3        | Output Clock for I2C bus #2 to host board                                                                                                                                                                                                        | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| I2C2_SDA    | BI        | 4.7K PU at<br>ESR<br>Note 3        | Bidirectional Data for I2C bus #2 to host board                                                                                                                                                                                                  | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| I2C3_SCL    | OUT       | 4.7K PU at<br>ESR<br>Note 3        | Output Clock for I2C bus #3 to host board                                                                                                                                                                                                        | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| Signal Name | Direction | Terminations      | Description                                     | Levels       | Impedance                                    |

|-------------|-----------|-------------------|-------------------------------------------------|--------------|----------------------------------------------|

| I2C3_SDA    | BI        | 4.7K PU at<br>ESR | Bidirectional Data for I2C bus #3 to host board | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers) |

|             |           | Note 3            |                                                 |              | +/-15% (outer layers                         |

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.