# cisco.

### **Cisco Embedded Service 6300 Series Router Hardware Technical Guide**

**First Published:** 2019-10-14 **Last Modified:** 2023-08-14

#### **Americas Headquarters**

Cisco Systems, Inc. 170 West Tasman Drive San Jose, CA 95134-1706 USA http://www.cisco.com Tel: 408 526-4000 800 553-NETS (6387) Fax: 408 527-0883 © 2019–2023 Cisco Systems, Inc. All rights reserved.

### CONTENTS

| CHAPTER 1 | Product Overview 1                                |

|-----------|---------------------------------------------------|

|           | Overview 1                                        |

|           | Audience 2                                        |

|           | General Description 2                             |

|           | ESR Board Layout and Dimensions 3                 |

|           | Board Without Cooling Plate 4                     |

|           | Board With Cooling Plate 7                        |

|           | External USB 3.0 10                               |

| CHAPTER 2 | Board-To-Board (BTB) Interface Connector 11       |

|           | BTB Interface Connector Overview 11               |

|           | ESR6300 Board-To-Board Connector (J1) 13          |

|           | Power and I/O Signals at the ESR BTB Connector 14 |

|           | Power Signals 15                                  |

|           | LED Control Signals 16                            |

|           | Gigabit Ethernet Port Signals 19                  |

|           | Module Interface Signals 20                       |

|           | External Port Signals 21                          |

|           | Miscellaneous Control Signals 23                  |

| CHAPTER 3 | Power and I/O Signals at the ESR BTB Connector 25 |

|           | Power and I/O Signals at the ESR BTB Connector 25 |

|           | Power Signals 25                                  |

|           | LED Control Signals 27                            |

|           | Gigabit Ethernet Port Signals 29                  |

|           | Module Interface Signals <b>31</b>                |

|           | External Port Signals <b>32</b>                                      |    |  |  |  |  |

|-----------|----------------------------------------------------------------------|----|--|--|--|--|

|           | Miscellaneous Control Signals 34                                     |    |  |  |  |  |

|           | _                                                                    |    |  |  |  |  |

| CHAPTER 4 | Implementation Options 37                                            |    |  |  |  |  |

|           | Thermal Design Considerations <b>37</b>                              |    |  |  |  |  |

|           | Validating a Thermal Solution <b>39</b>                              |    |  |  |  |  |

|           | Product Specifications <b>39</b>                                     |    |  |  |  |  |

|           | Power Requirements 40                                                |    |  |  |  |  |

|           | Power Over Ethernet (PoE) 41                                         |    |  |  |  |  |

|           | SFP Support 41                                                       |    |  |  |  |  |

|           | Supported 1000M SFP Modules 41                                       |    |  |  |  |  |

|           | Supported 100M Fast Ethernet SFP Modules 42                          |    |  |  |  |  |

|           | SFPs Supported in IOS XE 17.7.1 42                                   |    |  |  |  |  |

|           | LED Definitions 43                                                   |    |  |  |  |  |

|           | Block Diagrams 45                                                    |    |  |  |  |  |

|           | Mechanical and Environmental Testing 45                              |    |  |  |  |  |

|           | Overtemperature Detection 48                                         |    |  |  |  |  |

|           | Configuration Reset Overview 49                                      |    |  |  |  |  |

|           | Example Command Line Output <b>49</b>                                |    |  |  |  |  |

| CHAPTER 5 | Device Zeroization 51                                                |    |  |  |  |  |

|           | Device Zeroization 51                                                |    |  |  |  |  |

|           | Push Button 51                                                       |    |  |  |  |  |

|           | Important Notice about Zeroization <b>52</b>                         |    |  |  |  |  |

|           | Zeroization Details 53                                               |    |  |  |  |  |

|           | Zeroization is triggered after push button is pressed for 4 seconds: | 53 |  |  |  |  |

|           | Zeroization Performed on bootloader: 54                              |    |  |  |  |  |

|           | Zeroization Trigger 54                                               |    |  |  |  |  |

|           | To Trigger Zeroization 54                                            |    |  |  |  |  |

|           | Command Line Interface 55                                            |    |  |  |  |  |

|           | Microcontroller Unit (MCU) 55                                        |    |  |  |  |  |

| CHAPTER 6 | Appendix 57                                                          |    |  |  |  |  |

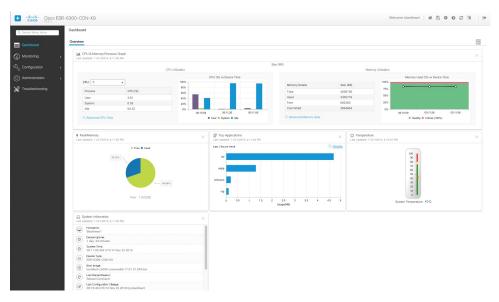

Web User Interface 57

Compliance and Safety Information 58

RoHS (Restriction of Hazardous Substances) 58

Related Documentation 59

Communications, Services, and Additional Information 59

Documentation Feedback 59

#### Contents

## **Product Overview**

This chapter contains the following sections:

- Overview, on page 1

- Audience, on page 2

- General Description, on page 2

- ESR Board Layout and Dimensions, on page 3

- External USB 3.0, on page 10

### **Overview**

This hardware technical guide provides a product description, specifications, and compliance information for the Cisco Embedded Service 6300 Series Router.

The documentation set for this product strives to use bias-free language. For purposes of this documentation set, bias-free is defined as language that does not imply discrimination based on age, disability, gender, racial identity, ethnic identity, sexual orientation, socioeconomic status, and intersectionality. Exceptions may be present in the documentation due to language that is hardcoded in the user interfaces of the product software, language used based on RFP documentation, or language that is used by a referenced third-party product.

The ESR6300 is a compact form factor embedded router module with a board size of 3.0" x 3.775"(76.2mm x 95.885mm). This module *may* fit in an enclosure that was *originally designed* for PC/104 modules with some additional adaptation. The more compact design simplifies integration and offers system integrators the ability to use the Cisco ESR6300 in a wide variety of embedded applications. The ESR card is available with a Cisco-designed cooling plate customized to the ESR, as well as without the cooling plate for system integrators who want to design their own custom thermal solution.

Note

More on the PC/104 standard can be found on the PC/104 Consortium website at https://pc104.org/

Ø

**Note** IOx development is not supported on the ESR6300. While this is platform independent code, it is unsupported and untested on this device.

The following table provides the hardware product IDs and brief descriptions for the boards.

| SKU             | Description                                                          | Ports/Module Interfaces      |

|-----------------|----------------------------------------------------------------------|------------------------------|

| ESR-6300-NCP-K9 | Embedded Router Board without a cooling plate. (NCP                  | 4 GE LAN ports               |

|                 | = No Cooling Plate)                                                  | 2 combo GE WAN ports         |

|                 |                                                                      | 1 USB 3.0 port               |

|                 |                                                                      | 1 async UART port            |

|                 |                                                                      | 1 alarm input                |

|                 |                                                                      | 1 Pluggable module interface |

| ESR-6300-CON-K9 | Embedded Router Board with cooling plate. (CON = Conduction cooled). | 4 GE LAN ports               |

|                 |                                                                      | 2 combo GE WAN ports         |

|                 |                                                                      | 1 USB 3.0 port               |

|                 |                                                                      | 1 async UART port            |

|                 |                                                                      | 1 alarm input                |

|                 |                                                                      | 1 Pluggable module interface |

## Audience

This guide is for system integrators who are integrating the Cisco ESR6300 into a custom end product.

## **General Description**

The ESR6300 is a ruggedized GigE Embedded Router platform for tactical, outdoor and mobile installations. Some of the key features are:

- Daughter board compact form factor 3.0" x 3.775"(76.2mm x 95.885mm)

- Class A EMC

- Industrial Temperature: -40C to +85C conduction plate temperature range

- 3.3V and 5V power inputs

- ARM Quad-Core A72 CPU, 1200MHz

- 4GB DDR4 memory capacity (32-bit + 4-bit ECC)

- 4GB usable (pSLC mode) eMMC flash

- Anti-counterfeit chip and Secure Boot

- Temperature Sensor

- Power consumption and voltage monitoring

- · Gigabit Ethernet LAN Switch for 4 external LAN ports

- · Gigabit Ethernet WAN PHY for 2 external WAN combo ports

- Interface to external features (requires additional circuitry):

- Four GE 10/100/1000 LAN Ports (with PoE support)

- Two GE combo (10/100/1000 and SFP) WAN Ports

- One UART interface (for RS232 async serial port with flow control)

- One UART Console interface (for CPU console access)

- RTC (Real Time Clock) with customer-provided battery backup

- Push Button that supports the Zeroize feature

- · One dry contact alarm input

- One USB 3.0 Host interface (for USB Flash Memory Device)

- One Cisco supported Pluggable Module Interface (for 4G/LTE module support)

Note

In order to recover the device from a complete zeroization, it must be configured with a Cisco supported USB3.0 device. Before triggering the zeroization process, make sure you are familiar with the topics in Device Zeroization, on page 51 and Configuration Reset Overview, on page 49!

Note

e The ESR6300 hardware uses GE as the name for the Gigabit Ethernet ports. However, Cisco IOS commands use Gi as the naming convention.

Software: Cisco IOS-XE

• IPSec

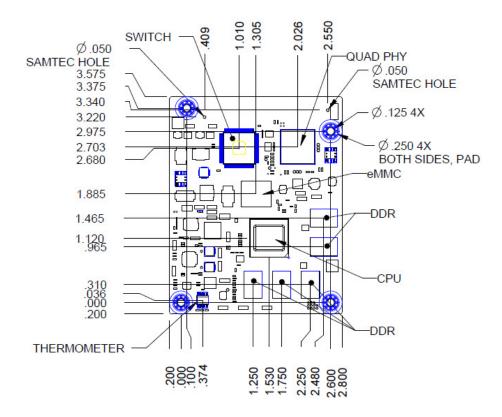

### ESR Board Layout and Dimensions

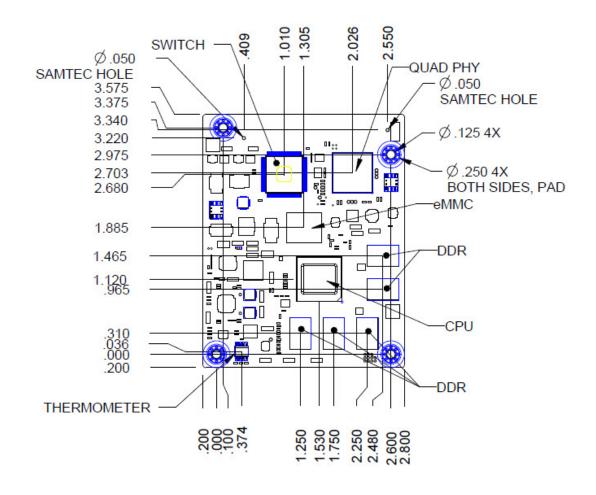

The following picture shows the ESR Board (left) with the cooling plate (right). The board dimensions are 3.0" x 3.775" (76.2mm x 95.885mm).

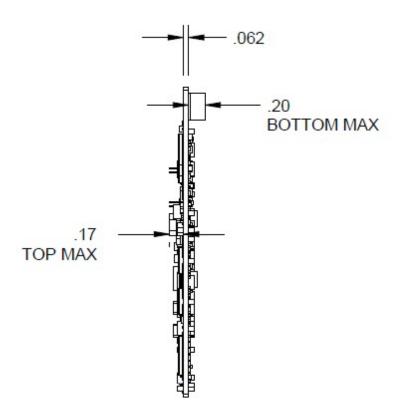

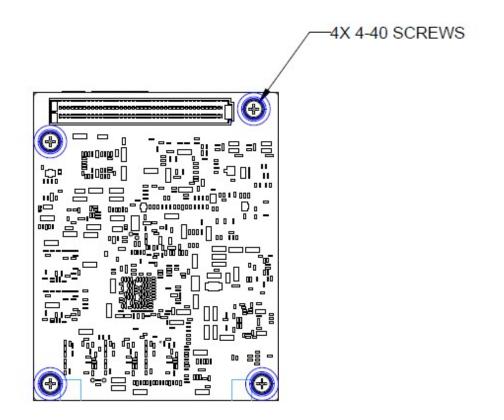

#### **Board Without Cooling Plate**

The following figures show the layout and dimensions of the ESR Board that is not equipped with the Cisco-designed cooling plate (ESR-6300-NCP-K9).

Note

Dimensions in inches. Tolerances (unless otherwise stated): .XX +/- 0.010, .XXX +/- 0.005

Figure 1: ESR-6300-NCP-K9

Figure 2: ESR-6300-NCP-K9

Figure 3: ESR-6300-NCP-K9

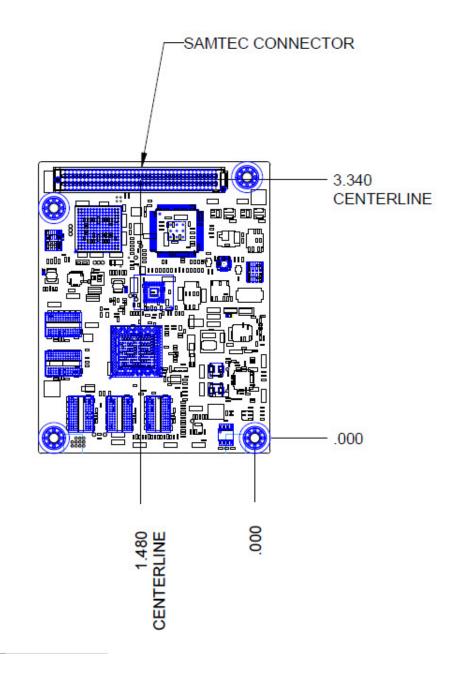

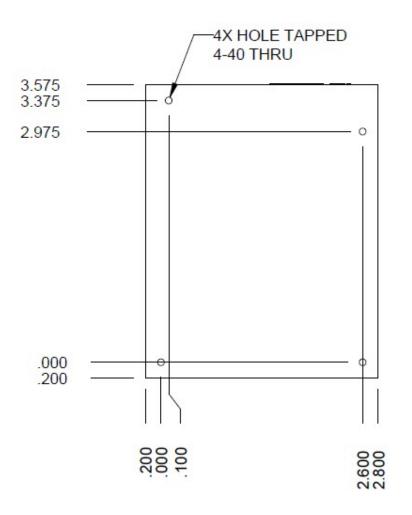

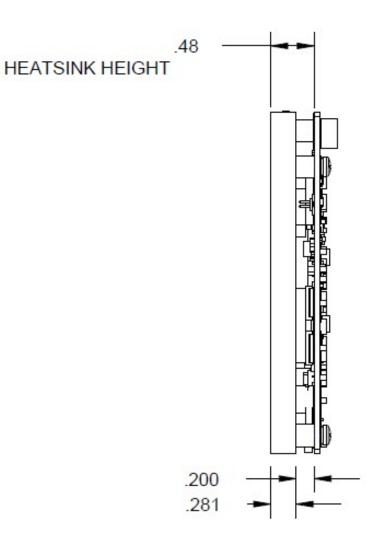

#### **Board With Cooling Plate**

The following figures show the layout and dimensions of the ESR Board that is equipped with the Cisco-designed cooling plate (ESR-6300-CON-K9).

Note

Dimensions in inches. Tolerances (unless otherwise stated): .XX +/- 0.010, .XXX +/- 0.005

Figure 4: ESR-6300-CON-K9

Figure 5: ESR-6300-CON-K9

Figure 6: ESR-6300-CON-K9

## **External USB 3.0**

There is support for an external USB3.0 type A device built into the USB controller.

Important

**nt** In order to recover the device from a complete zeroization, it must be configured with a Cisco supported USB3.0 device.

- Max 500mA at 5V

- Speed of operation: 1Mbps/12Mbps/480Mbps/5Gbps

- Storage only, not a data port

**Note** USBs with red/yellow port, for example the USBs with Sleep and Charge port, will not work on rommon prompt.

## **Board-To-Board (BTB) Interface Connector**

This chapter contains the following sections:

- BTB Interface Connector Overview, on page 11

- ESR6300 Board-To-Board Connector (J1), on page 13

- Power and I/O Signals at the ESR BTB Connector, on page 14

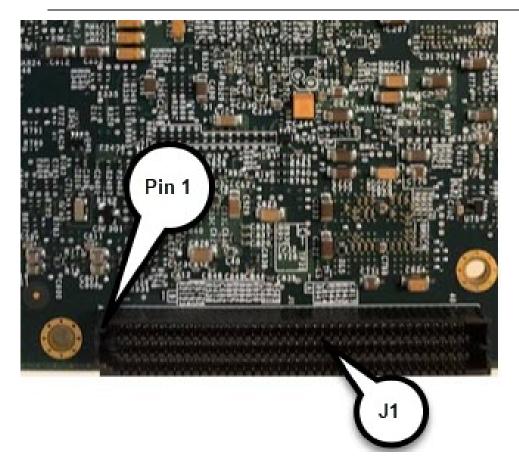

## **BTB Interface Connector Overview**

The board-to-board (BTB) connector provides the power input and the interface to external devices. This connector belongs to the SEARAY<sup>®</sup> Connector Series from SAMTEC. Depending on the mating connector selected by the integrator, the series supports a stacking height from 7mm to 18mm (not all increments are supported). The BTB connector on the ESR is the SAMTEC SEAF-40-05.0-S-06-2-A-K 240-pin female connector.

Complete information on the connector can be found at the Samtec website:

https://www.samtec.com/connectors/high-speed-board-to-board/high-density-arrays/searay

Note This figure is a partial view of the PCB to highlight the connector.

The following table lists the mating connector (SEAM lead style) options that are available to achieve specific stacking heights when coupled with the ESR (-05.0 SEAF lead style).

| Mating Connector | ESR Connector J1-05.0 |

|------------------|-----------------------|

| SEAM Lead Style  | SEAF Lead Style       |

| -02.0            | 7mm                   |

| -03.0            | 8mm                   |

| -03.5            | 8.5mm                 |

| -05.5            | N/A                   |

| -06.5            | 11.5mm                |

| -07.0            | 12mm                  |

| -09.0            | 14mm                  |

| Mating Connector  | ESR Connector J1-05.0 |  |  |

|-------------------|-----------------------|--|--|

| SEAM Lead Style   | SEAF Lead Style       |  |  |

| -11.0             | 16mm                  |  |  |

| -13.0(not tooled) | 18mm                  |  |  |

## ESR6300 Board-To-Board Connector (J1)

| PIN # | Row A     | Row B     | Row C     | Row D     | Row E          | Ro |

|-------|-----------|-----------|-----------|-----------|----------------|----|

| 1     | +5V       | +5V       | +5V       | +5V       | +5V            | +5 |

| 2     | +5V       | +5V       | +5V       | +5V       | +5V            | +5 |

| 3     | GND       | GND       | GND       | GND       | GND            | G  |

| 4     | GND       | GND       | GND       | GND       | GND            | G  |

| 5     | +3.3V     | +3.3V     | +3.3V     | +3.3V     | +3.3V          | R  |

| 6     | GND       | GND       | GND       | GND       | GND            | G  |

| 7     | P4_MDI3_N | GND       | P4_MDI2_N | GND       | PCIE_REFCLK_P  | P3 |

| 8     | P4_MDI3_P | GND       | P4_MDI2_P | GND       | PCIE_REFCLK_N  | G  |

| 9     | GND       | P4_MDI1_N | GND       | P4_MDI0_N | GND            | A  |

| 10    | GND       | P4_MDI1_P | GND       | P4_MDI0_P | GND            | PU |

| 11    | P3_MDI3_N | GND       | P3_MDI2_N | GND       | PIM_SGMII_RX_P | D  |

| 12    | P3_MDI3_P | GND       | P3_MDI2_P | GND       | PIM_SGMII_RX_N | PI |

| 13    | GND       | P3_MDI1_N | GND       | P3_MDI0_N | GND            | U  |

| 14    | GND       | P3_MDI1_P | GND       | P3_MDI0_P | GND            | U  |

| 15    | P2_MDI3_N | GND       | P2_MDI2_N | GND       | PIM_SGMII_TX_P | G  |

| 16    | P2_MDI3_P | GND       | P2_MDI2_P | GND       | PIM_SGMII_TX_N | C  |

| 17    | GND       | P2_MDI1_N | GND       | P2_MDI0_N | GND            | C  |

| 18    | GND       | P2_MDI1_P | GND       | P2_MDI0_P | GND            | C  |

| 19    | P1_MDI3_N | GND       | P1_MDI2_N | GND       | USBA_DP        | C  |

| 20    | P1_MDI3_P | GND       | P1_MDI2_P | GND       | USBA_DN        | G  |

| 21    | GND       | P1_MDI1_N | GND       | P1_MDI0_N | GND            | C  |

|       |           |           |           |           |                |    |

| PIN # | Row A           | Row B       | Row C           | Row D       | Row E       | Row   |

|-------|-----------------|-------------|-----------------|-------------|-------------|-------|

| 22    | GND             | P1_MDI1_P   | GND             | P1_MDI0_P   | GND         | CP_U  |

| 23    | PIM_USB3_TX_N   | GND         | PIM_USB3_RX_P   | GND         | PIM_USB2_DP | R0_L  |

| 24    | PIM_USB3_TX_P   | GND         | PIM_USB3_RX_N   | GND         | PIM_USB2_DN | R1_L  |

| 25    | GND             | USB3A_TX_N  | GND             | USB3A_RX_P  | GND         | C0_L  |

| 26    | GND             | USB3A_TX_P  | GND             | USB3A_RX_N  | GND         | C1_L  |

| 27    | SSD_TX_SERDES_P | GND         | SSD_RX_SERDES_P | GND         | PIM_UA2_TXD | GND   |

| 28    | SSD_TX_SERDES_N | GND         | SSD_RX_SERDES_N | GND         | PIM_UA2_RXD | P5_LI |

| 29    | GND             | SFP_2_TXD_P | GND             | SFP_2_RXD_P | GND         | SFP1  |

| 30    | GND             | SFP_2_TXD_N | GND             | SFP_2_RXD_N | GND         | P6_LI |

| 31    | P6_MDI3_N       | GND         | P6_MDI2_N       | GND         | PIM_GPS     | SFP2_ |

| 32    | P6_MDI3_P       | GND         | P6_MDI2_P       | GND         | ALM_LED_RED | GND   |

| 33    | GND             | P6_MDI1_P   | GND             | P6_MDI0_N   | GND         | AP_U  |

| 34    | GND             | P6_MDI1_N   | GND             | P6_MDI0_P   | GND         | AP_U  |

| 35    | P5_MDI2_N       | GND         | P5_MDI1_N       | GND         | VPN_LED_GRN | GND   |

| 36    | P5_MDI2_P       | GND         | P5_MDI1_P       | GND         | EVK_INT_L   | I2C3_ |

| 37    | GND             | P5_MDI3_N   | GND             | P5_MDI0_P   | GND         | I2C3_ |

| 38    | GND             | P5_MDI3_P   | GND             | P5_MDI0_N   | GND         | GND   |

| 39    | SFP_1_TXD_P     | GND         | SFP_1_RXD_P     | GND         | I2C2_SCL    | SYS_  |

| 40    | SFP_1_TXD_N     | GND         | SFP_1_RXD_N     | +1.8V_OUT   | I2C2_SDA    | SYS_  |

|       |                 |             |                 |             | 1           |       |

## Power and I/O Signals at the ESR BTB Connector

This section contains tables describing the control signals for different components. In the following tables, you will see the terms PU and PD. These stand for:

- PU = Pull-Up resistor

- PD = Pull-Down resistor

**Note** Differential pairs should be mostly routed on inner layers where the impedance tolerance is controlled better. Outer layers should only be used for very short differential pair traces (less than 0.25").

### **Power Signals**

| Signal Name          | Direction | Terminations                                            | Description                                                                                                                                                                                                                                                                                                                    | Levels       |

|----------------------|-----------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| +5V                  | IN        |                                                         | +5V Power Input to ESR board                                                                                                                                                                                                                                                                                                   | 5V DC        |

| +3.3V                | IN        |                                                         | +3.3V Power Input to ESR board                                                                                                                                                                                                                                                                                                 | 3.3V DC      |

| RTC_3.0V             | IN        | Series 1K resistor<br>required at Host<br><b>Note 6</b> | +3.0V RTC Battery Power Input to ESR board                                                                                                                                                                                                                                                                                     | 3.0V DC      |

| GND                  |           |                                                         | Ground                                                                                                                                                                                                                                                                                                                         | GND          |

| +1.8V_OUT            | OUT       | _                                                       | <ul> <li>+1.8V output from ESR board</li> <li>Caution         <ol> <li>1.8V source is only intended for use as a WAN port center tap voltage as shown in the reference design schematic. 50mA is the max that can be drawn from that 1.8V output.</li> </ol> </li> <li>See EVK Schematics below for further detail.</li> </ul> | 1.8V DC      |

| P3V3_TRIM            |           |                                                         | Trim signal to margin 3.3V +/-5%See reference design schematic for proper usage.(For test purposes only. Leave unconnected if not used.)                                                                                                                                                                                       | Passive      |

| DCIN_PWR_GOOD Note 8 | IN        | 50K PU at ESR<br>Note 1                                 | <ul> <li>External Power Supply Status Detect input (3.3V digital signal at the ESR connector).</li> <li>Can be used as an early power failure detect of the main power source.</li> <li>Active High (0 = Power Supply status is not good. 1 = Power Supply status is good.)</li> </ul>                                         | 3.3V<br>CMOS |

**Note 1**: Signal driver can be open drain with a strong pullup (4.7K to 10K), or can be driven by 3.3V push-pull levels. A pull-down is not allowed on this signal. Can be left unconnected if not used.

Note 6: Series 1K current-limiting resistor is required on the host board for the RTC 3.0V battery.

**Note 8**: (currently not supported by software for graceful shutdown, but could be in the future). Used for successful CPU power up and boot. Must be driven or pulled high at powerup, or left open (because it is already pulled up by the ESR and keeps it in a "good" state for proper power up and CPU boot if left open).

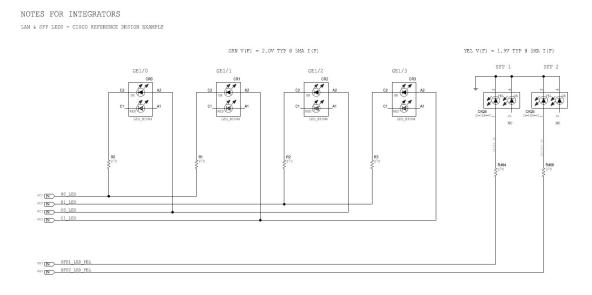

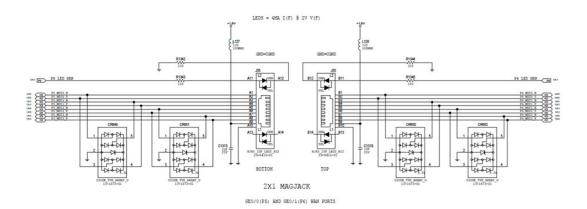

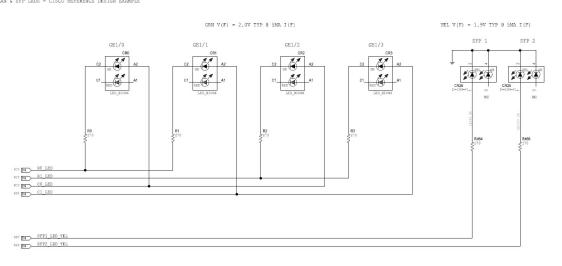

#### Figure 7: EVK Schematic

## **LED Control Signals**

| Signal Name   | Direction | Terminations                     | Description                           | Levels    |

|---------------|-----------|----------------------------------|---------------------------------------|-----------|

| SYS_LED_GRN_L | OUT       | 10K PD at ESR                    | System Green LED Enable (active low)  | 3.3V CMOS |

|               |           | Note 3                           |                                       |           |

|               |           | 270 Ohm series resistor at Host. |                                       |           |

|               |           | Note 7                           |                                       |           |

| SYS_LED_YEL_L | OUT       | 10K PD at ESR                    | System Yellow LED Enable (active low) | 3.3V CMOS |

|               |           | Note 3                           |                                       |           |

|               |           | 270 Ohm series resistor at Host. |                                       |           |

|               |           | Note 7                           |                                       |           |

| ALM_LED_RED   | OUT       | 1K PD at ESR                     | Alarm Red LED Enable (active high)    | 3.3V CMOS |

|               |           | Note 3                           |                                       |           |

|               |           | 270 Ohm series resistor at Host. |                                       |           |

|               |           | Note 7                           |                                       |           |

| VPN_LED_GRN   | OUT       | 4.7K PU at ESR                   | VPN Green LED Enable (active high)    | 3.3V CMOS |

|               |           | Note 3                           |                                       |           |

|               |           | 270 Ohm series resistor at Host. |                                       |           |

|               |           | Note 7                           |                                       |           |

| Signal Name  | Direction | Terminations                        | Description                                                                                                                                            | Levels    |  |

|--------------|-----------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|

| R0_LED       | OUT       | 270 Ohm series resistor at<br>Host. | Row 0 LED control for LAN Ports GE 1/1 and GE 1/0.<br>(controls cathode-side of 2 single-color LEDs).                                                  | 3.3V CMOS |  |

|              |           | Note 7                              | Cathode-side LED Enable (driven by Ethernet Switch on ESR) - Active Low.                                                                               |           |  |

|              |           |                                     | Tie to Cathode side of two single-color Green LEDs through a resistor to each (e.g., 270 ohms for a 5mA forward current on each of the 2 LEDs).        |           |  |

| C0_LED       | OUT       | 4.7K PD at ESR<br>Note 3            | Column 0 LED control for LAN Ports GE 1/2 and GE 1/0.                                                                                                  | 3.3V CMOS |  |

|              |           |                                     | (controls anode-side of 2 single-color LEDs).                                                                                                          |           |  |

|              |           |                                     | (Anode-side LED Enable (driven by Ethernet Switch on ESR) - Active high.                                                                               |           |  |

|              |           |                                     | Tie <b>DIRECTLY</b> to Anode side of two single-color Green LEDs.                                                                                      |           |  |

| R1_LED       | OUT       | 270 Ohm series resistor at<br>Host. | Row 1 LED control for LAN Ports <b>GE 1/3</b> and <b>GE 1/2</b> .                                                                                      | 3.3V CMOS |  |

|              |           | Note 7                              | (controls cathode-side of 2 single-color LEDs).                                                                                                        |           |  |

|              |           |                                     | Cathode-side LED Enable (driven by Ethernet Switch on ESR) - Active Low.                                                                               |           |  |

|              |           |                                     | Tie to Cathode side of two single-color Green LEDs through a resistor to each (for example, 270 ohms for a 5mA forward current on each of the 2 LEDs). |           |  |

| C1_LED       | OUT       | 4.7K PD at ESR<br>Note 3            | Column 1 LED control for LAN Ports GE 1/3 and GE 1/1.                                                                                                  | 3.3V CMOS |  |

|              |           |                                     | (controls anode-side of 2 single-color LEDs).                                                                                                          |           |  |

|              |           |                                     | (Anode-side LED Enable (driven by Ethernet Switch on ESR) - Active high.                                                                               |           |  |

|              |           |                                     | Tie <b>DIRECTLY</b> to Anode side of two single-color Green LEDs.                                                                                      |           |  |

| P5_LED_GRN   | OUT       | 270 Ohm series resistor at Host.    | WAN Copper Port (GE 0/0) LED Enable (controlled<br>by Ethernet PHY on ESR) - Active High                                                               | 3.3V CMOS |  |

|              |           | Note 7                              |                                                                                                                                                        |           |  |

| SFP1_LED_YEL | OUT       | 270 Ohm series resistor at<br>Host. | WAN SFP Port (SFP 0/0) LED Enable (controlled by<br>Ethernet PHY on ESR) - Active High                                                                 | 3.3V CMOS |  |

|              |           | Note 7                              |                                                                                                                                                        |           |  |

| Signal Name  | Direction | Terminations                                         | Description                                                                              | Levels    |

|--------------|-----------|------------------------------------------------------|------------------------------------------------------------------------------------------|-----------|

| P6_LED_GRN   | OUT       | 270 Ohm series resistor at<br>Host.<br>Note 7        | WAN Copper Port (GE 0/1) LED Enable (controlled<br>by Ethernet PHY on ESR) - Active High | 3.3V CMOS |

| SFP2_LED_YEL | OUT       | 270 Ohm series resistor at<br>Host.<br><b>Note 7</b> | WAN SFP Port (SFP 0/1) LED Enable (controlled by Ethernet PHY on ESR) - Active High      | 3.3V CMOS |

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed, as they are necessary during system reset to configure bootup settings. However, after any system reset (after system boots up), those signals are free to be driven and free to change states.

**Note 7**: Series current-limiting resistor is required on host board for the LED driving signals. LEDs on host board should be chosen so that they operate well at 5mA forward current.

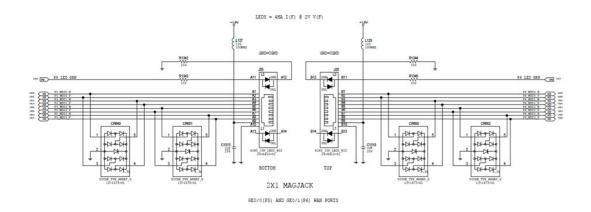

See the following figure for a design reference.

#### Figure 8: LAN and SFP LED Reference Design

The Marvell Ethernet PHY chip set controls the LEDs, simply implement as shown in the reference design schematics. The Marvell chip minimizes the number of control lines by row and column to convey the correct link state and activity indication for all 4 ports. Cisco software does not control the ethernet port LEDs directly.

## **Gigabit Ethernet Port Signals**

| Signal Name           | Direction | Terminations                           | Description                                                                                    | Levels        | Impedance                                                             |

|-----------------------|-----------|----------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------|

| SFP_2_TXD_[ P/N ]     | OUT       | Series Caps at<br>SFP<br><b>Note 2</b> | Port 6 (WAN SFP 0/1) SFP Transmit<br>Differential Pair                                         | 1.6V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_2_RXD_[ P/N ]     | IN        | Series Caps at<br>SFP<br><b>Note 2</b> | Port 6 (WAN SFP 0/1) SFP Receive<br>Differential Pair                                          | 2.1V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_1_TXD_[ P/N ]     | OUT       | Series Caps at<br>SFP<br><b>Note 2</b> | Port 5 (WAN SFP 0/0) SFP Transmit<br>Differential Pair                                         | 1.6V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_1_RXD_[ P/N ]     | IN        | Series Caps at<br>SFP<br><b>Note 2</b> | Port 5 (WAN SFP 0/0) SFP Receive<br>Differential Pair                                          | 2.1V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P6_MDI[30]_[ P/N<br>] | BI        |                                        | Port 6 (WAN GE 0/1) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 2.8V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P5_MDI[30]_[ P/N<br>] | BI        |                                        | Port 5 (WAN GE 0/0) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 2.8V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P4_MDI[30]_[ P/N<br>] | BI        |                                        | Port 4 (LAN GE 1/3) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P3_MDI[30]_[ P/N<br>] | BI        |                                        | Port 3 (LAN GE 1/2) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P2_MDI[30]_[ P/N<br>] | BI        |                                        | Port 2 (LAN GE 1/1) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P1_MDI[30]_[ P/N<br>] | BI        |                                        | Port 1 (LAN GE 1/0) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

### **Module Interface Signals**

| Signal Name              | Direction | Terminations                                                                                                  | Description                                                                       | Levels           | Impedance                                                            |

|--------------------------|-----------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| PCIE_REFCLK_[<br>P/N ]   | OUT       | If not used, keep open.<br>The router will disable<br>the PCIE reference<br>clock when no PCIe is<br>present. | PCIe 100MHz Differential Pair<br>Reference Clock for Pluggable<br>or SSD Module   | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_SGMII_TX_[<br>P/N ]  | OUT       | Series Caps at PIM<br>Note 2                                                                                  | SGMII Transmit Differential Pair<br>for Pluggable Module (Can be<br>PCIe TX also) | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_SGMII_RX_[<br>P/N ]  | IN        | Series Caps at ESR<br>Note 2                                                                                  | SGMII Receive Differential Pair<br>for Pluggable Module (Can be<br>PCIe RX also)  | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_USB3_TX_[<br>P/N ]   | OUT       | Series Caps at ESR<br>Note 2                                                                                  | USB 3.0 Transmit Differential<br>Pair for Pluggable Module                        | 1.2V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_USB3_RX_[<br>P/N ]   | IN        | Series Caps at PIM<br>Note 2                                                                                  | USB 3.0 Receive Differential<br>Pair for Pluggable Module                         | 1.2V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_USB2_[<br>DP/DN ]    | BI        | 2x 15K PD at ESR                                                                                              | USB 2.0 Differential Pair for<br>Pluggable Module                                 | 3.6V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_UA2_TXD              | OUT       | 10K PU at PIM<br>Note 3                                                                                       | UART2 Transmit Data for<br>Pluggable Module                                       | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_UA2_RXD              | IN        | 4.7K PU at ESR<br>Note 3                                                                                      | UART2 Receive Data for<br>Pluggable Module                                        | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| SSD_TX_SERDES_[<br>P/N ] | OUT       | Series Caps at Host<br>Note 4                                                                                 | SERDES Transmit Differential<br>Pair for SSD Module (Can be<br>SATA or PCIe)      | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| Signal Name              | Direction | Terminations                                                                                                             | Description                                                                                                                      | Levels           | Impedance                                                            |

|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| SSD_RX_SERDES_[<br>P/N ] | IN        | Series Caps at ESR<br><b>Note 2</b>                                                                                      | SERDES Receive Differential<br>Pair for SSD Module (Can be<br>SATA or PCIe)                                                      | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_PWR_EN               | OUT       | 1K PD at PIM<br>Note 3                                                                                                   | Power Enable signal for the<br>Pluggable Module.<br>Active high (0 = disable<br>Pluggable power. 1 = Enable<br>Pluggable power.) | 3.3V CMOS        |                                                                      |

| PIM_GPS                  | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | GPS Pulse Per Second Timing<br>signal from Pluggable Module                                                                      | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.

Note 4: Series caps required on the host board for these SERDES signals.

### **External Port Signals**

| Signal Name         | Direction | Terminations                         | Description                                                      | Levels          | Impedance                                                           |

|---------------------|-----------|--------------------------------------|------------------------------------------------------------------|-----------------|---------------------------------------------------------------------|

| USB3A_TX_[<br>P/N ] | OUT       | Series Caps at ESR<br>Note 2         | USB 3.0 Transmit Differential Pair<br>for External USB Host Port | 1.2V Max<br>USB | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| USB3A_RX_[<br>P/N ] | IN        | Series Caps at Host<br><b>Note 4</b> | USB 3.0 Receive Differential Pair<br>for External USB Host Port  | 1.2V Max<br>USB | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| USBA_[ DP/DN<br>]   | BI        | 2x 15K PD at ESR                     | USB 2.0 Differential Pair for<br>External USB Host Port          | 3.6V Max<br>USB | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| Signal Name | Direction | Terminations                    | Description                                                                                                                                        | Levels    | Impedance                                                            |

|-------------|-----------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------|

| USBA_5V_EN  | OUT       | 1K PD at ESR<br>Note 3          | Enable 5V output of the external<br>USB Host Port.<br>Active High (0 = disable 5V USB<br>output. 1 = enable USB 5V output)                         | 3.3V CMOS |                                                                      |

| USBA_OC_L   | IN        | 10K PU at Host<br>Note 5        | Over Current Detect of the external<br>USB Host Port.<br>Active Low (0 = USB host port 5V<br>is in overcurrent condition. 1 =<br>Normal Operation) | 3.3V CMOS |                                                                      |

| CP_UA0_DTR  | OUT       | 10K PU at Host<br>Note 5        | UART0 DTR flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_DSR  | IN        | 4.7K PU at ESR<br><b>Note 3</b> | UART0 DSR flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_RTS  | OUT       | 10K PU at Host<br>Note 5        | UART0 RTS flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_CTS  | IN        | 4.7K PU at ESR<br>Note 3        | UART0 CTS flow control signal for<br>external RS232 Serial Port                                                                                    | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_TXD  | OUT       | 10K PU at Host<br>Note 5        | UART0 Transmit Data for external<br>RS232 Serial Port                                                                                              | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| CP_UA0_RXD  | IN        | 4.7K PU at ESR<br><b>Note 3</b> | UART0 Receive Data for external<br>RS232 Serial Port                                                                                               | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| AP_UA0_TXD  | OUT       | 1K PD at ESR<br>Note 3          | Transmit Data for Console Port                                                                                                                     | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| AP_UA0_RXD  | IN        | 100K PU at Host<br>Note 5       | Receive Data for Console Port                                                                                                                      | 3.3V CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| Signal Name  | Direction | Terminations                                                                                                             | Description                                                                                                                                                 | Levels    | Impedance |

|--------------|-----------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|

| ALM_IN_L     | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | Alarm Input (3.3V digital signal at<br>the ESR connector).<br>Active Low (0 = external alarm port<br>is closed. 1 = external alarm port is<br>open circuit) | 3.3V CMOS |           |

| PUSHBUTTON_L | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | Pushbutton Detect Input (3.3V<br>digital signal at the ESR connector).<br>Active Low (0 = pushbutton is<br>closed. 1 = pushbutton is open).                 | 3.3V CMOS |           |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.

Note 4: Series caps required on the host board for these SERDES signals.

**Note 5**: PU/PD are required on the host board for these signals.

#### **Miscellaneous Control Signals**

| Signal Name | Direction | Terminations                | Description                                                                                                                                                                                                                                      | Levels       | Impedance                                                            |

|-------------|-----------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------|

| EVK_INT_L   | IN        | 4.7K PU at<br>ESR<br>Note 3 | Reserved for Interrupt input to the ESR CPU from<br>the host board. Currently not used by the Cisco<br>Software to detect interrupts from the host<br>motherboard. User should leave this signal<br>unconnected, as the ESR provides the pullup. | 3.3V<br>CMOS |                                                                      |

| I2C2_SCL    | OUT       | 4.7K PU at<br>ESR<br>Note 3 | Output Clock for I2C bus #2 to host board                                                                                                                                                                                                        | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| I2C2_SDA    | BI        | 4.7K PU at<br>ESR<br>Note 3 | Bidirectional Data for I2C bus #2 to host board                                                                                                                                                                                                  | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| I2C3_SCL    | OUT       | 4.7K PU at<br>ESR<br>Note 3 | Output Clock for I2C bus #3 to host board                                                                                                                                                                                                        | 3.3V<br>CMOS | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| Signal Name | Direction | Terminations                | Description                                     | Levels | Impedance                                                            |

|-------------|-----------|-----------------------------|-------------------------------------------------|--------|----------------------------------------------------------------------|

| I2C3_SDA    | BI        | 4.7K PU at<br>ESR<br>Note 3 | Bidirectional Data for I2C bus #3 to host board | CMOS   | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+/-15% (outer layers |

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.

UNAFIER U

## Power and I/O Signals at the ESR BTB Connector

This chapter contains the following sections:

- Power and I/O Signals at the ESR BTB Connector, on page 25

- Power Signals, on page 25

- LED Control Signals, on page 27

- Gigabit Ethernet Port Signals, on page 29

- Module Interface Signals, on page 31

- External Port Signals, on page 32

- Miscellaneous Control Signals, on page 34

### Power and I/O Signals at the ESR BTB Connector

This section contains tables describing the control signals for different components. In the following tables, you will see the terms PU and PD. These stand for:

- PU = Pull-Up resistor

- PD = Pull-Down resistor

Differential pairs should be mostly routed on inner layers where the impedance tolerance is controlled better. Outer layers should only be used for very short differential pair traces (less than 0.25").

## **Power Signals**

| Signal Name | Direction | Terminations                                            | Description                                | Levels  |

|-------------|-----------|---------------------------------------------------------|--------------------------------------------|---------|

| +5V         | IN        | _                                                       | +5V Power Input to ESR board               | 5V DC   |

| +3.3V       | IN        | —                                                       | +3.3V Power Input to ESR board             | 3.3V DC |

| RTC_3.0V    | IN        | Series 1K resistor<br>required at Host<br><b>Note 6</b> | +3.0V RTC Battery Power Input to ESR board | 3.0V DC |

| Signal Name          | Direction | Terminations                   | Description                                                                                                                                                                                                                                                                                                                    | Levels  |  |  |

|----------------------|-----------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| GND                  | —         |                                | Ground                                                                                                                                                                                                                                                                                                                         | GND     |  |  |

| +1.8V_OUT            | OUT       |                                | <ul> <li>+1.8V output from ESR board</li> <li>Caution         <ol> <li>1.8V source is only intended for use as a WAN port center tap voltage as shown in the reference design schematic. 50mA is the max that can be drawn from that 1.8V output.</li> </ol> </li> <li>See EVK Schematics below for further detail.</li> </ul> | 1.8V DC |  |  |

| P3V3_TRIM            |           |                                | Trim signal to margin 3.3V +/-5%       Pass         See reference design schematic for proper usage.       (For test purposes only. Leave unconnected if not used.)                                                                                                                                                            |         |  |  |

| DCIN_PWR_GOOD Note 8 | IN        | 50K PU at ESR<br><b>Note 1</b> | <ul> <li>External Power Supply Status Detect input (3.3V digital signal at the ESR connector).</li> <li>Can be used as an early power failure detect of the main power source.</li> <li>Active High (0 = Power Supply status is not good. 1 = Power Supply status is good.)</li> </ul>                                         |         |  |  |

**Note 1**: Signal driver can be open drain with a strong pullup (4.7K to 10K), or can be driven by 3.3V push-pull levels. A pull-down is not allowed on this signal. Can be left unconnected if not used.

Note 6: Series 1K current-limiting resistor is required on the host board for the RTC 3.0V battery.

**Note 8**: (currently not supported by software for graceful shutdown, but could be in the future). Used for successful CPU power up and boot. Must be driven or pulled high at powerup, or left open (because it is already pulled up by the ESR and keeps it in a "good" state for proper power up and CPU boot if left open).

#### Figure 9: EVK Schematic

## **LED Control Signals**

| Signal Name   | Direction | Terminations                     | Description                                                                                                                                     | Levels    |

|---------------|-----------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| SYS_LED_GRN_L | OUT       | 10K PD at ESR                    | System Green LED Enable (active low)                                                                                                            | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| SYS_LED_YEL_L | OUT       | 10K PD at ESR                    | System Yellow LED Enable (active low)                                                                                                           | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| ALM_LED_RED   | OUT       | 1K PD at ESR                     | Alarm Red LED Enable (active high)                                                                                                              | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| VPN_LED_GRN   | OUT       | 4.7K PU at ESR                   | VPN Green LED Enable (active high)                                                                                                              | 3.3V CMOS |

|               |           | Note 3                           |                                                                                                                                                 |           |

|               |           | 270 Ohm series resistor at Host. |                                                                                                                                                 |           |

|               |           | Note 7                           |                                                                                                                                                 |           |

| R0_LED        | OUT       | 270 Ohm series resistor at       | Row 0 LED control for LAN Ports GE 1/1 and GE 1/0.                                                                                              | 3.3V CMOS |

|               |           | Host.                            | (controls cathode-side of 2 single-color LEDs).                                                                                                 |           |

|               |           | Note 7                           | Cathode-side LED Enable (driven by Ethernet Switch on ESR) - Active Low.                                                                        |           |

|               |           |                                  | Tie to Cathode side of two single-color Green LEDs through a resistor to each (e.g., 270 ohms for a 5mA forward current on each of the 2 LEDs). |           |

| •            | 2   | Terminations                        | Description                                                                                                                                            | Levels    |

|--------------|-----|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| C0_LED       | OUT | 4.7K PD at ESR<br>Note 3            | Column 0 LED control for LAN Ports GE 1/2 and GE 1/0.                                                                                                  | 3.3V CMOS |

|              |     |                                     | (controls anode-side of 2 single-color LEDs).                                                                                                          |           |

|              |     |                                     | (Anode-side LED Enable (driven by Ethernet Switch on ESR) - Active high.                                                                               |           |

|              |     |                                     | Tie <b>DIRECTLY</b> to Anode side of two single-color Green LEDs.                                                                                      |           |

| R1_LED       | OUT | 270 Ohm series resistor at Host.    | Row 1 LED control for LAN Ports <b>GE 1/3</b> and <b>GE 1/2</b> .                                                                                      | 3.3V CMOS |

|              |     | Note 7                              | (controls cathode-side of 2 single-color LEDs).                                                                                                        |           |

|              |     |                                     | Cathode-side LED Enable (driven by Ethernet Switch on ESR) - Active Low.                                                                               |           |

|              |     |                                     | Tie to Cathode side of two single-color Green LEDs through a resistor to each (for example, 270 ohms for a 5mA forward current on each of the 2 LEDs). |           |

| C1_LED       | OUT | 4.7K PD at ESR<br>Note 3            | Column 1 LED control for LAN Ports <b>GE 1/3</b> and <b>GE 1/1</b> .                                                                                   | 3.3V CMOS |

|              |     |                                     | (controls anode-side of 2 single-color LEDs).                                                                                                          |           |

|              |     |                                     | (Anode-side LED Enable (driven by Ethernet Switch on ESR) - Active high.                                                                               |           |

|              |     |                                     | Tie <b>DIRECTLY</b> to Anode side of two single-color Green LEDs.                                                                                      |           |

| P5_LED_GRN   | OUT | 270 Ohm series resistor at Host.    | WAN Copper Port (GE 0/0) LED Enable (controlled by Ethernet PHY on ESR) - Active High                                                                  | 3.3V CMOS |

|              |     | Note 7                              |                                                                                                                                                        |           |

| SFP1_LED_YEL | OUT | 270 Ohm series resistor at<br>Host. | WAN SFP Port (SFP 0/0) LED Enable (controlled by<br>Ethernet PHY on ESR) - Active High                                                                 | 3.3V CMOS |

|              |     | Note 7                              |                                                                                                                                                        |           |

| P6_LED_GRN   | OUT | 270 Ohm series resistor at<br>Host. | WAN Copper Port (GE 0/1) LED Enable (controlled<br>by Ethernet PHY on ESR) - Active High                                                               | 3.3V CMOS |

|              |     | Note 7                              |                                                                                                                                                        |           |

| SFP2_LED_YEL | OUT | 270 Ohm series resistor at<br>Host. | WAN SFP Port (SFP 0/1) LED Enable (controlled by<br>Ethernet PHY on ESR) - Active High                                                                 | 3.3V CMOS |

|              |     | Note 7                              |                                                                                                                                                        |           |

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration

of the ESR CPU and should not be changed, as they are necessary during system reset to configure bootup settings. However, after any system reset (after system boots up), those signals are free to be driven and free to change states.

**Note 7**: Series current-limiting resistor is required on host board for the LED driving signals. LEDs on host board should be chosen so that they operate well at 5mA forward current.

See the following figure for a design reference.

#### Figure 10: LAN and SFP LED Reference Design

NOTES FOR INTEGRATORS

Note

The Marvell Ethernet PHY chip set controls the LEDs, simply implement as shown in the reference design schematics. The Marvell chip minimizes the number of control lines by row and column to convey the correct link state and activity indication for all 4 ports. Cisco software does not control the ethernet port LEDs directly.

### **Gigabit Ethernet Port Signals**

| Signal Name       | Direction | Terminations                    | Description                                            | Levels        | Impedance                                                             |

|-------------------|-----------|---------------------------------|--------------------------------------------------------|---------------|-----------------------------------------------------------------------|

| SFP_2_TXD_[ P/N ] | OUT       | Series Caps at<br>SFP<br>Note 2 | Port 6 (WAN SFP 0/1) SFP Transmit<br>Differential Pair |               | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_2_RXD_[ P/N ] | IN        | Series Caps at<br>SFP<br>Note 2 | Port 6 (WAN SFP 0/1) SFP Receive<br>Differential Pair  | 2.1V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| Signal Name           | Direction | Terminations                           | Description                                                                                    | Levels        | Impedance                                                             |

|-----------------------|-----------|----------------------------------------|------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------|

| SFP_1_TXD_[ P/N ]     | OUT       | Series Caps at<br>SFP<br><b>Note 2</b> | Port 5 (WAN SFP 0/0) SFP Transmit<br>Differential Pair                                         | 1.6V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| SFP_1_RXD_[ P/N ]     | IN        | Series Caps at<br>SFP<br>Note 2        | Port 5 (WAN SFP 0/0) SFP Receive<br>Differential Pair                                          | 2.1V Max LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P6_MDI[30]_[ P/N<br>] | BI        |                                        | Port 6 (WAN GE 0/1) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 2.8V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P5_MDI[30]_[ P/N<br>] | BI        |                                        | Port 5 (WAN GE 0/0) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 2.8V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P4_MDI[30]_[ P/N<br>] | BI        |                                        | Port 4 (LAN GE 1/3) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P3_MDI[30]_[ P/N<br>] | BI        |                                        | Port 3 (LAN GE 1/2) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P2_MDI[30]_[ P/N<br>] | BI        |                                        | Port 2 (LAN GE 1/1) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

| P1_MDI[30]_[ P/N<br>] | BI        |                                        | Port 1 (LAN GE 1/0) MDI Differential<br>Pairs for 10/100/1000 Gigabit Ethernet<br>Copper Ports | 1.4V Max MDI  | 100 Ohm Differential<br>+/-10% (inner layers)<br>+/-15% (outer layers |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

# **Module Interface Signals**

| Signal Name              | Direction | Terminations                                                                                                  | Description                                                                       | Levels           | Impedance                                                            |

|--------------------------|-----------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| PCIE_REFCLK_[<br>P/N ]   | OUT       | If not used, keep open.<br>The router will disable<br>the PCIE reference<br>clock when no PCIe is<br>present. | PCIe 100MHz Differential Pair<br>Reference Clock for Pluggable<br>or SSD Module   | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_SGMII_TX_[<br>P/N ]  | OUT       | Series Caps at PIM<br>Note 2                                                                                  | SGMII Transmit Differential Pair<br>for Pluggable Module (Can be<br>PCIe TX also) | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_SGMII_RX_[<br>P/N ]  | IN        | Series Caps at ESR<br>Note 2                                                                                  | SGMII Receive Differential Pair<br>for Pluggable Module (Can be<br>PCIe RX also)  | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_USB3_TX_[<br>P/N ]   | OUT       | Series Caps at ESR<br>Note 2                                                                                  | USB 3.0 Transmit Differential<br>Pair for Pluggable Module                        | 1.2V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_USB3_RX_[<br>P/N ]   | IN        | Series Caps at PIM<br>Note 2                                                                                  | USB 3.0 Receive Differential<br>Pair for Pluggable Module                         | 1.2V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_USB2_[<br>DP/DN ]    | BI        | 2x 15K PD at ESR                                                                                              | USB 2.0 Differential Pair for<br>Pluggable Module                                 | 3.6V Max USB     | 90 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_UA2_TXD              | OUT       | 10K PU at PIM<br>Note 3                                                                                       | UART2 Transmit Data for<br>Pluggable Module                                       | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| PIM_UA2_RXD              | IN        | 4.7K PU at ESR<br>Note 3                                                                                      | UART2 Receive Data for<br>Pluggable Module                                        | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

| SSD_TX_SERDES_[<br>P/N ] | OUT       | Series Caps at Host<br>Note 4                                                                                 | SERDES Transmit Differential<br>Pair for SSD Module (Can be<br>SATA or PCIe)      | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| Signal Name              | Direction | Terminations                                                                                                             | Description                                                                                                                      | Levels           | Impedance                                                            |

|--------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------|

| SSD_RX_SERDES_[<br>P/N ] | IN        | Series Caps at ESR<br>Note 2                                                                                             | SERDES Receive Differential<br>Pair for SSD Module (Can be<br>SATA or PCIe)                                                      | 1.6V Max<br>LVDS | 100 Ohm Differential<br>+/-10% (inner layers)<br>+-15% (outer layers |

| PIM_PWR_EN               | OUT       | 1K PD at PIM<br>Note 3                                                                                                   | Power Enable signal for the<br>Pluggable Module.<br>Active high (0 = disable<br>Pluggable power. 1 = Enable<br>Pluggable power.) | 3.3V CMOS        |                                                                      |

| PIM_GPS                  | IN        | 4.7K PU at ESRIf not<br>used, keep open. The<br>router will pull it up and<br>keep it in an idle state.<br><b>Note 3</b> | GPS Pulse Per Second Timing<br>signal from Pluggable Module                                                                      | 3.3V CMOS        | 50 Ohm Single-Ended<br>+/-10% (inner layers)<br>+-15% (outer layers  |

**Note 2**: Series AC-coupling caps to SERDES signals already exist on Cisco ESR, PIM or SFP module. No need to add any more.

**Note 3**: PU/PD to signals already exist on Cisco ESR, PIM, SFP, or SSD modules. No need to add any more. If you do add redundant parallel PU/PD, it should be weak (10K to 100K). Do not add a strong PU/PD for the purpose of overriding it to the opposite state. Some existing ESR PUs and PDs set the default configuration of the ESR CPU and should not be changed.