# **Channel APC**

This chapter describes channel APC.

- Channel APC, on page 1

- How channel APC works, on page 3

- Enable channel APC, on page 3

- Disable channel APC, on page 4

- Pause channel APC, on page 4

- Resume channel APC, on page 5

- Set target PSD for channel APC, on page 5

- Configure input amplifier, on page 6

- View channel APC information, on page 6

### **Channel APC**

Channel APC is an optical application that maintains all optical channels at a consistent Power Spectral Density (PSD) target by dynamically regulating optical components. This ensures a flat spectrum before transmission over the fiber span.

The purpose of the Channel APC control loop is to equalize the Power Spectral Density (PSD) of all channels to a defined Channel Target PSD.

### Channel Target PSD:

This is an optical-line-control (OLC) configuration parameter that defines the desired PSD level for all channels. By default, this value is –20 dBm, measured in dBm/12.5GHz.

### • Optical Channel Monitor (OCM):

The OCM device provides readings of the channel power spectral density, dividing the spectrum into 6.25GHz slices. The Channel PSD is calculated based on readings from the OCM and is averaged over the central 25GHz bandwidth.

### • Input Channel Acceptance:

Before a channel is transmitted, its input PSD is evaluated against the Channel PSD target plus a defined margin (PSD\_MARGIN). A channel is accepted and unblocked by the Wavelength Blocker (WB) if its estimated PSD after initial amplification and WB insertion loss is greater than the target PSD plus the margin.

### • PSD Control Loop:

Once a channel is accepted, the WB attenuation for the channel's slices is adjusted from maximum to an initial value calculated to bring the Channel PSD near or slightly below the target. The control loop then periodically monitors the Channel PSD at the WB output. If the discrepancy between the measured PSD and the target PSD exceeds a defined threshold (PSD Correction Tolerance), the WB attenuation is corrected incrementally. The loop continues until the discrepancy is small, applying a final correction equal to the residual error. The loop regulates again if the discrepancy later exceeds the threshold.

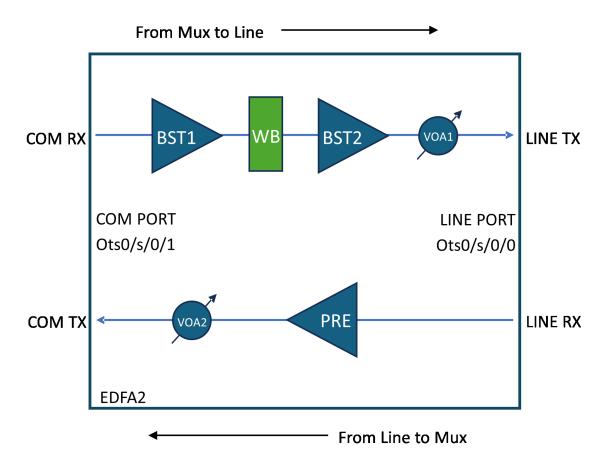

This diagram shows the NCS1K14-EDFA2 line card optical layout. Optical components controlled by channel APC are highlighted in green.

Figure 1: NCS1K14-EDFA2 line card optical layout

### **Channel Acceptance and Blocking Criteria**

- Acceptance:

- By default, WB blocks all C-band spectrum.

- Channels must have PSD after WB (0 attenuation) higher than the target PSD plus a 0.5 dBm/12.5 GHz margin to be accepted.

### • Blocking:

• Channels with WB attenuation at 0 dB and PSD lower than target PSD minus 2.0 dBm/12.5 GHz tolerance are blocked by the control loop.

### **How channel APC works**

### **Summary**

Channel APC control loop equalizes the Power Spectral Density (PSD) of all channels to a defined Channel Target PSD.

### Workflow

These stages describe channel APC process:

- 1. Input and Amplification:

- Channels enter via Controller Ots0/<slot>/0/1 (COM-RX).

- First stage amplification by BST1.

- Channel APC equalizes PSD across channels before the second stage amplifier (BST2 + VOA1).

- 2. Wavelength Blocker (WB):

- Controls attenuation per 6.25 GHz slice (0 to 15 dB or full block).

- Channel power equalization is based on a configurable Channel Target PSD (default: -20 dBm/12.5 GHz).

- PSD is averaged over the central 25 GHz bandwidth from OCM measurements.

- 3. Channel APC Control:

- When enabled, Channel APC overrides manual WB attenuation settings.

- OSC channel is excluded from Channel APC control.

# **Enable channel APC**

This topic describes how to enable channel APC.

This task describes how to configure channel APC. This configuration is in this topic:

· Enable channel APC

### **Procedure**

Use the following commands to enable channel APC:

```

configure

optical-line-control

controller ots <Rack/Slot/Instance/Port>

channel-apc flat-psd-eq-mode

commit

end

```

## **Disable channel APC**

This topic describes how to disable channel APC.

This task describes how to configure channel APC. This configuration is in this topic:

· Disable channel APC

### **Procedure**

Use the following commands to disable channel APC:

```

configure

optical-line-control

controller ots <Rack/Slot/Instance/Port>

no channel-apc flat-psd-eq-mode

commit

end

```

# **Pause channel APC**

This topic describes how to pause channel APC.

This task describes how to configure channel APC. This configuration is in this topic:

· Pause channel APC

### **Procedure**

Use the following commands to pause channel APC:

```

configure

optical-line-control

controller ots <Rack/Slot/Instance/Port>

channel-apc-pause

commit

end

```

### **Resume channel APC**

This topic describes how to resume channel APC.

This task describes how to configure channel APC. This configuration is in this topic:

· Resume channel APC

### **Procedure**

Use the following commands to resume channel APC:

```

configure

optical-line-control

controller ots <Rack/Slot/Instance/Port>

no channel-apc-pause

commit

end

```

# **Set target PSD for channel APC**

This topic describes how to set target PSD for channel APC.

This task describes how to configure channel APC. This configuration is in this topic:

· Set target PSD for chanel

### **Procedure**

Use the following commands to set target PSD for a channel:

```

configure

optical-line-control

controller ots <Rack/Slot/Instance/Port>

psd-target <value in dBm/12.5GHz>

commit

end

```

### **Example:**

This sample configuration sets the target PSD to -22 dBm/12.5 GHz:

```

configure

optical-line-control

controller ots 0/0/0/0

psd-target -220

commit

end

```

# **Configure input amplifier**

This topic describes how to configure channel APC.

In scenarios with low total input power, you must adjust BST1 amplifier gain and range. This table shows some typical scenarios:

Table 1: BST1 Amplifier Configuration

| Optical Interfaces | Spacing    | BST1 Total Input<br>Power [dBm] | BST1 range | BST1 Gain [dB] |

|--------------------|------------|---------------------------------|------------|----------------|

| 400ZR              | 75 GHz     | 0.2~2.3                         | Extended   | 18.5           |

| mix 400ZR/800ZR    | 75/150 GHz | -5~0.2                          | Extended   | 18.5           |

| 800ZR              | 150 GHz    | 0.6~1.2                         | Extended   | 18.5           |

| DCI                | 75 GHz     | 6~6.9                           | Normal     | 8              |

| mix DCI/DCI-1      | 75/150 GHz | 5.3~6.9                         | Normal     | 8              |

| DCI-1              | 150 GHz    | 9.8~10.4                        | Normal     | 8              |

| DCI-2 (CIM8)       | 150 GHz    | 11.4~12.2                       | Normal     | 8              |

### **Procedure**

Use the following commands to adjust BST1 amplifier gain and gain range:

```

configure

controller ots <Rack/Slot/Instance/Port>

ingress-ampli-gain-range <normal|extended>

ingress-ampli-gain <gain_value_in_tenths_of_dB>

commit

end

```

### **Example:**

This sample configuration sets BST1 gain range to extended and the gain to 19.5 dB:

```

configure

controller ots 0/0/0/1

ingress-ampli-gain-range extended

ingress-ampli-gain 195

commit

end

```

## **View channel APC information**

This task describes how to view channel APC information.

These tables describe the different parameters and status values in the output of the show command.

Table 2: Channel APC parameter definitions

| Parameter                       | Description                                                                                                         |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Controller                      | Identifier of the optical controller managing the channel, formatted as Ots0/slot/interface/port.                   |  |  |  |

| Internal Status                 | Current state of the Channel APC control loop, e.g., IDLE means regulation is complete and stable.                  |  |  |  |

| Input Gain                      | Gain value (in dB) applied by the first stage amplifier (BST1) to the input signal.                                 |  |  |  |

| Input Gain Range                | Gain range mode of the BST1 amplifier, e.g., Normal or Extended, indicating the amplifier's operating range.        |  |  |  |

| Input Gain Range Min - Max      | Minimum and maximum gain values (in dB) for the BST1 amplifier in the current gain range.                           |  |  |  |

| Last Correction                 | Timestamp of the last adjustment made by the Channel APC control loop to equalize channel power.                    |  |  |  |

| Output PSD Target               | Target Power Spectral Density (PSD) value (in dBm/12.5 GHz) that the Channel APC aims to maintain for all channels. |  |  |  |

| <b>PSD Correction Tolerance</b> | Allowed deviation margin (in dB) from the target PSD before the Channel APC initiates a correction.                 |  |  |  |

### Table 3: Channel APC status definitions

| Status      | Description                                                                                  |  |  |

|-------------|----------------------------------------------------------------------------------------------|--|--|

| BLOCKED     | Triggered by amplifier safety events (APR, OSRI), RX-LOS alarms, or OTS controller shutdown. |  |  |

|             | The following reasons can cause this status:                                                 |  |  |

|             | • INPUT-EDFA-OSRI-ENABLED                                                                    |  |  |

|             | • OUTPUT-EDFA-OSRI-ENABLED                                                                   |  |  |

|             | • INPUT-EDFA-RX-LOS                                                                          |  |  |

|             | • OUTPUT-OTS-SHUTDOWN                                                                        |  |  |

|             | • INPUT-OTS-SHUTDOWN                                                                         |  |  |

| D. L. LOTTO |                                                                                              |  |  |

| PAUSED      | Regulation paused via channel-apc-pause command; no adjustments occur.                       |  |  |

| IDLE        | Regulation complete; all channels meet target PSD within tolerance.                          |  |  |

| REGULATING  | Active regulation in progress to correct PSD discrepancies.                                  |  |  |

### Table 4: Channel APC table parameters

| Parameter  | Description                                                               |

|------------|---------------------------------------------------------------------------|

| Controller | Ots-Och r/s/i/p/ <channel-id> Channel in input to the COM-RX</channel-id> |

| Center Frequency | Central frequency of the channel                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Width            | Width of the channel                                                                                                                                                                            |

| Status           | Status of the Channel, see the Channel APC per-channel status definitions table.                                                                                                                |

| Spectrum         | Set of spectrum slices belonging to the channel                                                                                                                                                 |

| Input PSD        | Channel Input power in term of PSD at COM-RX input port                                                                                                                                         |

| Input Power      | Channel Input power at COM-RX input port                                                                                                                                                        |

| Channel PSD      | Channel power in term of PSD after the WB block. It should be next to the PSD target less than the <i>PSD Correction Tolerance</i> parameter shown by the command                               |

| Channel Power    | Channel power after the WB block                                                                                                                                                                |

| PSD Discrepancy  | Current error margin between the <i>Channel PSD</i> and the <i>Configured Target PSD</i> . It the value increases above the <i>PSD Correction Tolerance</i> , a new regulation sequence starts. |

| Attenuation      | The attenuation value configured on the WB to reach the target.                                                                                                                                 |

### Table 5: Channel APC per-channel status definitions

| Channel Status | Description                                                                     |

|----------------|---------------------------------------------------------------------------------|

| Active         | Channel is managed and matches target PSD at WB output.                         |

| Not Active     | Channel power insufficient to reach target PSD; channel is blocked or inactive. |

| Regulating     | Channel is currently undergoing PSD adjustment.                                 |

| Out Of Range   | Channel PSD too high or too low to be active even with max or zero attenuation. |

### **Procedure**

To view channel APC information, use the show olc channel-apc regulation-info command.

### **Example:**

RP/0/RP0/CPU0:IOS#show olc channel-apc regulation-info

Thu Jul 17 16:06:13.213 CEST

Controller : Ots0/0/0/0

Internal Status : IDLE

Input Gain : 8.0 dB

Input Gain Range : Normal

Input Gain Range Min - Max

: 5.0 - 11.0 dB

Last Correction : 2025-07-17 14:23:18

Output PSD Target : -20.0 dBm/12.5GHz

PSD Correction Tolerance

| Controller<br>Channel      | Center<br>Channel    | Width<br>PSD         | Status<br>Attenuation | Spectrum     | Input         | Input  |

|----------------------------|----------------------|----------------------|-----------------------|--------------|---------------|--------|

| PSD                        | Frequency<br>Power   | (GHz)<br>Discrepancy | (dB)                  | 6.25 GHz     | PSD           | Power  |

| (dBm/12.5GHz)              | (THz)<br>(dBm)       | (dBm)                |                       | Slices Range | (dBm/12.5GHz) | (dBm)  |

| Ots-Och0/0/0/0/1<br>-50.00 | 196.100000<br>-50.00 | 75.000<br>-          | Not Active<br>25.00   | 779 - 790    | -50.00        | -50.00 |

| Ots-Och0/0/0/0/2<br>-19.97 | 196.025000<br>-14.00 | 75.000<br>0.03       | Active 0.10           | 767 - 778    | -24.22        | -18.10 |

| Ots-Och0/0/0/0/3<br>-50.00 | 195.950000<br>-50.00 | 75.000<br>-          | Not Active<br>25.00   | 755 - 766    | -50.00        | -50.00 |

: 0.3 dB

#### Note

APC periodically monitors the per channel Power Spectral Density (PSD) discrepancy. If the measured discrepancy exceeds the **PSD Correction Tolerance**, the APC initiates regulation on the Line Controller to reduce each channel's discrepancy below the defined tolerance. This regulation ensures a flat spectrum before the EDFA facing the LINE port.

- The regulation process may take a few seconds to complete.

- During this time, the APC status transitions and eventually reaches the final state **IDLE**.

- The values displayed by the command show olc channel-apc controller Ots0/0/0/0 regulation-info reflect the state of the LC at the moment the command is executed.

- Because the regulation is ongoing during this period, some values shown may already reflect the final regulated state, while others may not yet have updated to the final values.

This behavior is important to understand when interpreting the output of the channel APC regulation status, as transient discrepancies in the displayed data can occur during the regulation process.

View channel APC information