Fehlerstruktur für Paritätsfehler des Cisco 7200

Inhalt

Einführung

In diesem Dokument werden die Schritte zur Fehlerbehebung und Isolierung der Komponenten oder Komponenten eines Cisco 7200 erläutert, die bei der Erkennung einer Reihe von Paritätsfehlermeldungen fehlschlagen. Wir empfehlen, dass Sie die Fehlerbehebung bei Router-Abstürzen und PMPEs (Processor Memory Parity Errors) lesen, bevor Sie mit diesem Dokument fortfahren.

Hinweis: Die Informationen in diesem Dokument basieren auf den Cisco Routern der Serie 7200.

Voraussetzungen

Anforderungen

Für dieses Dokument bestehen keine besonderen Voraussetzungen.

Verwendete Komponenten

Dieses Dokument ist nicht auf bestimmte Software- und Hardwareversionen beschränkt.

Die in diesem Dokument enthaltenen Informationen wurden aus Geräten in einer bestimmten Laborumgebung erstellt. Alle in diesem Dokument verwendeten Geräte haben mit einer leeren (Standard-)Konfiguration begonnen. Wenn Sie in einem Live-Netzwerk arbeiten, stellen Sie sicher, dass Sie die potenziellen Auswirkungen eines Befehls verstehen, bevor Sie es verwenden.

Konventionen

Weitere Informationen zu Dokumentkonventionen finden Sie in den Cisco Technical Tips Conventions.

NPE-Paritätsfehleranalyse (Network Processing Engine)

In diesem Diagramm werden die Schritte beschrieben, um festzustellen, welches Teil oder welche Komponente eines Cisco 7200 fehlschlägt, wenn Sie eine Reihe von Paritätsfehlermeldungen identifizieren.

Hinweis: Erfassen und notieren Sie die show tech-support-Ausgabe und die Konsolenprotokolle, und sammeln Sie alle crashinfo-Dateien bei Paritätsfehlerereignissen.

Erkennung von NPE-Paritätsfehlern und Meldungen

Dieser Abschnitt enthält Blockdiagramme für den NPE und wo diese Systeme Paritätsfehler erkennen. Nachfolgend finden Sie eine Beschreibung der einzelnen Fehlermeldungstypen.

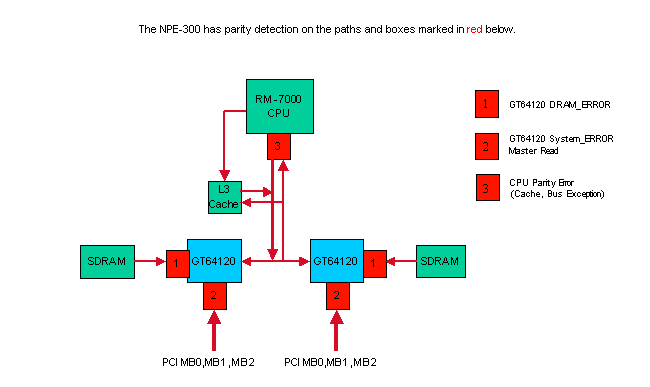

Paritätsfehler im NPE-300

Der NPE-300 verwendet Paritätsprüfungen im gemeinsamen Speicher (SDRAM), im PCI-Bus und in der externen CPU-Schnittstelle, um das System vor Fehlfunktionen durch Bitfehler zu schützen. Die Paritätsprüfung kann einen einzelnen Bit-Fehler mithilfe einer einfachen Methode erkennen. Hinzufügen eines Check-Bit pro acht Datenbits. Wenn bei der Übertragung der Daten zwischen Hardwarekomponenten ein Bitfehler erkannt wird, werden die fehlerhaften Daten vom System verworfen. Einzelbitfehler an einer beliebigen Stelle im Diagramm oben führen dazu, dass der Router zurückgesetzt wird.

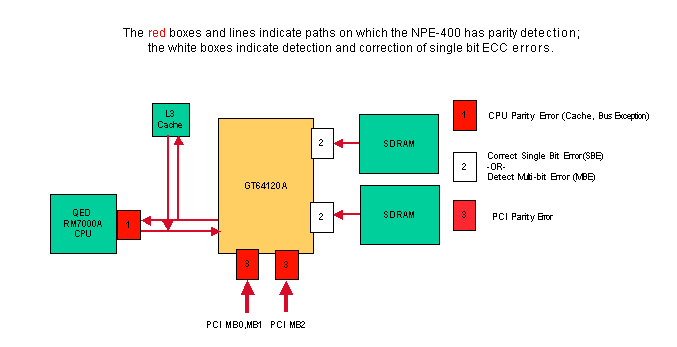

NPE-400 Parität/ECC-Erkennung

Der NPE-400 verwendet Single-Bit-Fehlerkorrektur und Multi-Bit-Fehlererkennung ECC (Error Code Correction) für gemeinsam genutzten Speicher (SDRAM). Um die Systemverfügbarkeit im NPE-400 zu erhöhen, korrigiert ECC Single-Bit-Fehler im SDRAM, damit das System ohne Zurücksetzen und ohne Ausfallzeiten normal funktioniert. Weitere Informationen zur Verbesserung der Systemverfügbarkeit durch ECC finden Sie auf der Seite Erhöhte Netzwerkverfügbarkeit.

Ein Multi-Bit-Fehler im SDRAM bewirkt, dass der Router mit einer Cache-Fehlerausnahme oder einem Busfehler zurückgesetzt wird. Der Rest des Speichers und der Busse im System verwendet Single-Bit-Paritätserkennung. Einzelbitfehler bei 1 und 3 im obigen Diagramm bewirken, dass der Router zurückgesetzt wird.

Paritätsfehler auf dem C7200-Router

Mehrere der Geräte zur Paritätsprüfung am C7200/NPE-Router können Daten mit schlechter Parität für alle Lese- oder Schreibvorgänge melden. Hier finden Sie eine Beschreibung der verschiedenen Fehlermeldungen, die auf einem C7200/NPE-System gemeldet werden:

DRAM-Fehler GT64010/GT64120

Dieser Fehler wird gemeldet, wenn ein GT64120-Systemcontroller einen Paritätsfehler beim Lesen von SDRAM erkennt:

%ERR-1GT64120 (PCI0):Fatal error, Memory parity error (external) GT=0xB4000000, cause=0x0100E283, mask=0x0ED01F00, real_cause=0x00000200 Bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x1C000000

Ersetzen Sie den SDRAM nach einem zweiten Ausfall. Wenn der Fehler weiterhin besteht, ersetzen Sie den NPE.

Hinweis: Bei älteren NPEs (NPE-100/150/200), die die GT64010-Controller verwenden, sieht der Fehler wie folgt aus:

%ERR-1-GT64010: Fatal error, Memory parity error (external) cause=0x0300E283, mask=0x0CD01F00, real_cause=0x00000200 bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x00000000

Der GT64010-Controller verwendet Dynamic RAM (DRAM) und nicht SDRAM. In diesem Fall ersetzen Sie das DRAM nach einem zweiten Fehler. Wenn der Fehler weiterhin besteht, ersetzen Sie den NPE.

GT64010/GT64120-Systemparitätsfehler Master Read

Ein Paritätsfehler in Master Read ist ein Paritätsfehler, der durch den Zugriff auf eine PCI-Bridge (Peripheral Component Interconnect) ausgelöst wird. Hier ein Beispiel für die Ausgabe von Paritätsfehlern:

%ERR-1-GT64120 (PCI0):Fatal error, Parity error on master read GT=B4000000, cause=0x0110E083, mask=0x0ED01F00, real_cause=0x00100000 Bus_err_high=0x00000000, bus_err_low=0x00000000, addr_decode_err=0x00000470 %ERR-1-SERR: PCI bus system/parity error %ERR-1-FATAL: Fatal error interrupt, No reloading Err_stat=0x81, err_enable=0xFF, mgmt_event=0x40

Ersetzen Sie die entsprechende Komponente nach einem zweiten Fehler. Das Systembrücke-Dump zeigt an, welche Komponente ersetzt werden soll.

System bridge dump:

Bridge 1, for PA bay 1, 3 and 5. Handle=1

DEC21150 bridge chip, config=0x0

(0x1C):sec status, io base =0x83A09141

Detected Parity Error on secondary bus

Data Parity Detected on secondary bus

(0x20):mem base & limit =0x4AF04880

Diese Tabellen geben an, welche Komponente ein mögliches Problem mit der Fehlermeldungsausgabe hat.

NPE-100/150/200:

| Bridge-Nummer | Wofür ist die Bridge? | Paritätsfehler beim primären Bus | Paritätsfehler im sekundären Bus |

|---|---|---|---|

| Bridge 0 | Downstream MB0 zu MB1 0 | Ersetzen Sie den NPE. | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen |

| Bridge 1 | Upstream-MB1 in MB0 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | Ersetzen Sie den NPE. |

| Brücke 2 | Downstream MB0 zu MB2 | Ersetzen Sie den NPE. | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen |

| Bridge 3 | Upstream-MB2 in MB0 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | Ersetzen Sie den NPE. |

NPE-175/225/300/400/NSE-1:

| Bridge-Nummer | Wofür ist die Bridge? | Paritätsfehler beim primären Bus | Paritätsfehler im sekundären Bus |

|---|---|---|---|

| Bridge 0 | Für PA-Schacht 0 (E/A-Karte, PCMCIA, Schnittstellen) | Ersetzen Sie den NPE. | Ersetzen Sie NPE. Ersetzen Sie die E/A-Karte, wenn diese noch vorhanden ist. Ersetzen Sie das Chassis, falls vorhanden. |

| Bridge 1 | Für PA-Schacht 1, 3 und 5 | Ersetzen Sie den NPE. | Ersetzen Sie den NPE. falls vorhanden, Chassis ersetzen |

| Brücke 2 | Für PA-Einschub 2, 4 und 6 | Ersetzen Sie den NPE. | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen |

Alle C7200-Router:

| Bridge-Nummer | Wofür ist die Bridge? | Paritätsfehler beim primären Bus | Paritätsfehler im sekundären Bus |

|---|---|---|---|

| Brücke 4 | Port-Adapter 1 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | PA 1 ersetzen; falls vorhanden, Chassis ersetzen |

| Brücke 5 | Port-Adapter 2 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | PA 2 ersetzen; falls vorhanden, Chassis ersetzen |

| Bridge 6 | Port-Adapter 3 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | PA 3 ersetzen; falls vorhanden, Chassis ersetzen |

| Brücke 7 | Port-Adapter 4 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | PA 4 ersetzen; falls vorhanden, Chassis ersetzen |

| Brücke 8 | Port-Adapter 5 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | PA 5 ersetzen; falls vorhanden, Chassis ersetzen |

| Brücke 9 | Port-Adapter 6 | Ersetzen Sie NPE. falls vorhanden, Chassis ersetzen | PA 6 ersetzen; falls vorhanden, Chassis ersetzen |

CPU-Paritätsfehler

Wie bei allen Computer- und Netzwerkgeräten ist der NPE anfällig für das seltene Auftreten von Paritätsfehlern im Prozessorspeicher. Paritätsfehler können dazu führen, dass das System zurückgesetzt wird, und es kann sich um ein vorübergehendes Single Event Upset (SEU oder Soft Error) handeln, oder es kann mehrere Male (häufig als "harte Fehler" bezeichnet) aufgrund einer beschädigten Hardware auftreten. Weitere Informationen zu SEUs finden Sie auf der Seite Erhöhte Netzwerkverfügbarkeit. Ein CPU-Paritätsfehler wird gemeldet, wenn die CPU einen Paritätsfehler beim Zugriff auf die Cache-Speicher des Prozessors erkennt (L1, L2 oder, falls vorhanden, L3).

Hier sind vier Beispiele für diesen Fehlertyp:

Beispiel 1:

Error: SysAD, data cache, fields: data, 1st dword

Physical addr(21:3) 0x195BE88,

Virtual address is imprecise.

Imprecise Data Parity Error

Imprecise Data Parity Error

Der NPE verfügt über einen R7K-Prozessor mit nicht blockierendem Cache. Non-Blocking-Cache: Wenn er eine Anweisung ausführt, Daten in ein Register zu laden, und sich diese Daten nicht im L1-Cache befinden, lädt die CPU die Daten aus einem Cache mit niedrigerer Reihenfolge oder aus SDRAM-Daten. Die CPU blockiert die Ausführung weiterer Anweisungen nur, wenn ein anderer Cache-Fehler vorliegt oder eine andere Anweisung von den geladenen Daten abhängt. Dies kann den Prozessor erheblich beschleunigen und die Leistung verbessern, kann aber auch zu unpräzisen Paritätsfehlern führen. Ein ungenauer Paritätsfehler besteht darin, dass die CPU Informationen ohne Blockierung liest und später feststellt, dass in der zugeordneten Cache-Zeile ein Paritätsfehler aufgetreten ist. Der R7K-Prozessor kann uns nicht genau sagen, welche Anweisung ausgeführt wurde, als die Cache-Leitung geladen wurde. Aus diesem Grund nennen wir es einen ungenauen Paritätsfehler.

Auch wenn Systeme Fehlercode-Korrektur (ECC) verwenden, ist es immer noch möglich, einen gelegentlichen Paritätsfehler zu erkennen, wenn in den 64-Bit-Daten aufgrund eines harten Cache-Fehlers mehr als ein einziger Fehler aufgetreten ist.

Ein Paritätsfehler tritt auf, wenn ein Signal-Bitwert von seinem ursprünglichen Wert (0 oder 1) in den entgegengesetzten Wert geändert wird. Dieser Fehler kann entweder aufgrund eines weichen oder eines harten Paritätsfehlers auftreten.

Weiche Paritätsfehler treten aufgrund eines externen Einflusses auf den Speicher des Geräts auf, der den Bitwert auf der aktuellen Ebene ändert. Diese Art von Problem ist vorübergehend und tritt nicht erneut auf. Strikte Paritätsfehler treten auf, wenn der Bitwert durch den Speicher selbst geändert wird, weil der Speicher beschädigt ist. In diesem Fall tritt das Problem jedes Mal auf, wenn der Speicherbereich verwendet wird, d. h. das Problem kann sich innerhalb von ein paar Tagen bis eine Woche mehrmals wiederholen.

Beispiel 2:

Error: SysAD, instr cache, fields: data, 1st dword

Physical addr(21:3) 0x000000,

virtual addr 0x6040BF60, vAddr(14:12) 0x3000

virtual address corresponds to main:text, cache word 0

Low Data High Data Par Low Data High Data Par

L1 Data: 0:0xAE620068 0x8C830000 0x00 1:0x50400001 0xAC600004 0x01

2:0xAC800000 0x00000000 0x02 3:0x1600000B 0x00000000 0x01

Low Data High Data Par Low Data High Data Par

DRAM Data: 0:0xAE620068 0x8C830000 0x00 1:0x50400001 0xAC600004 0x01

2:0xAC800000 0x00000000 0x02 3:0x1600000B 0x00000000 0x01

Beispiel 3:

Cache Err Reg = 0xE4588D10 Data reference, Secondary/Sys intf cache, Data field error Error on 1st doubleword on System interface No errors in addition to instr error Data phy addr that caused last parity or bus error: 0x1E84040C

Beispiel 4 (nur NPE-300 und NPE-400):

%CERF-3-RECOVER: PC=0x604F136C, Origin=L3 Data ,PhysAddr=0x013CEFD0

oder

%SYS-2-CERF_ABORT: Reason=0xEE23, PC=0x604629C8, Origin=L3 Data, Phys Addr=0x0287A4E8

Beide Meldungen oben werden mit einem "Cache Error Recovery Function (CERF) Report" wie folgt begleitet:

CERFa[1 ] 05:25:36 MET Tue Jul 9 2002: result=0xEE23; instr_pos=-2; rpl_off=1 CERFb[1 ] PC =604629C8; ORGN=L3 Data; PRID=00002710; PHYA=0287A4E8 CERFc[1 ] SREG=3400E105; CAUS=00000400; DEA0=0287A4E8; ECC =00000000 CERFd[1 ] CERR=E447A4EA; EPC =606361F8; DEA1=02517058; INFO=00000000 CERFe[1 ] CACHE=28FF78B4 62B36D98 02020684 00000E17 00000030 00000001 61F2934C 3EDA025D CERFe[1 ] SDRAM=28FF78B4 62B36D98 02020684 00000E17 00000030 00000001 61F2934C 3EDA025D CERFg[1 ] CXT =00000000; XCXT=00000000; BVAD=00000008; PFCL=00000000 CERFh[1 ] ISeq: 0045182B; 1060000E; 2C4203E9; 92430028; 38420001; 30630005 CERFi[1 ] o0 $3 ....; beq....; sltiu $2 ....; lbu $3, 0x0028($18); xori $2....; andi $3 ....;* CERFj[1 ] ; ; ; 6287A4E8; ; ; CERFk[1 ] ResumptionCode= 0x92430028; 0x0000000F; 0x42000018 CERFl[1 ] Instr's checked=4; diags=0x00000158,0x00040000,3600,1,0 CERFm[1 ] BaseRegLost later/off: 0/0 times; StoredValueLost: 0 times CERFn[1 ] INFO=00000000; CNFG=5061F4BB; ICTL=00000000 Initial Register Values CERFs00[1 ] $0=00000000 AT=61A30000 v0=00000001 v1=00000002 CERFs04[1 ] a0=28FF8728 a1=00003A98 a2=00000000 a3=00000007 CERFs08[1 ] t0=00000000 t1=3400E101 t2=606381E0 t3=FFFF00FF CERFs12[1 ] t4=606381C8 t5=000005D4 t6=00000008 t7=61C50000 CERFs16[1 ] s0=6189C188 s1=00000000 s2=6287A4C0 s3=00003A98 CERFs20[1 ] s4=61BD57B0 s5=00000006 s6=00000000 s7=61BD6C60 CERFs24[1 ] t8=60634788 t9=00000000 k0=621A8374 k1=6063EA40 CERFs28[1 ] gp=61A33B20 sp=61E28678 s8=00000000 ra=60462CA4 1 Cache error exceptions already reported

Sie sehen die obigen Protokolle, wenn CERF auf einem NPE-300 oder NPE-400 aktiviert ist und ein Paritätsfehler auftritt. Weitere Informationen zum CERF finden Sie im Abschnitt "Lösungen" unten.

Lösungen

Bei Auftreten solcher Fehler empfiehlt sich die folgende Vorgehensweise:

-

Überwachen Sie die betroffene Hardware, um festzustellen, ob das gleiche Problem erneut auftritt. Ist dies nicht der Fall, handelt es sich um eine vorübergehende Single Event Upset (SEU), und Sie müssen keine Maßnahmen ergreifen.

-

Falls das Problem nicht erneut auftritt, ist der Befehl zur Umgehung/Deaktivierung des L3-Cache eine Option, die die Auswirkungen des Problems verringern kann. Dieser Befehl ist nur auf den folgenden Plattformen verfügbar:

-

7200 mit Prozessor-Engine NPE-300, NPE-400 oder NSE-1

-

7400 mit Prozessor-Enginer NSE-1

Da der NPE-300 den ECC-Speicher nicht unterstützt, ist diese Funktion besonders wichtig, um die Systemverfügbarkeit zu erhöhen und diese Paritätsfehler ohne Serviceunterbrechung zu beheben. Dadurch werden viele weiche Paritätsfehler behoben. Der Nachteil ist, dass das System leicht von der Leistung betroffen ist, wenn der L3-Cache deaktiviert ist. Die Leistungsabnahme liegt je nach Systemkonfiguration zwischen 1 % und 10 %. Die Syntax für die Verwendung dieses Befehls hängt von der Cisco IOS-Softwareversion ab.

-

Der Befehl L3-Deaktivierung im Cache finden Sie in Cisco IOS Software Releases 12.3(5a) und höher. Es wird auch in 12.1(22)E verfügbar sein. In diesen Versionen ist der L3-Cache standardmäßig deaktiviert, sodass keine Aktion erforderlich ist, um diese Funktion zu nutzen. Der L3-Cache kann mit dem Befehl no cache L3 disable erneut aktiviert werden.

-

Der L3-Bypass-Befehl für den Cache finden Sie in den Cisco IOS Software Releases 12.2(6)S, 12.2(6)B, 12.2(8)BC1b, 12.0(20)SP, 12.2(6)PB, 12.2(2)DD2, 12.0(20)ST3 12.0(21)S, 12.1(11)EC, 12.2(7)T, 12.1(13) und 12.2(7) oder höher und 12.1(11)E bis 12.1(21)E. Dieser Befehl ist standardmäßig deaktiviert.

Um die Umgehung des L3-Cache zu aktivieren, geben Sie im Konfigurationsmodus Folgendes ein:

Router(config)#cache L3 bypass

Um die Umgehung des L3-Cache zu deaktivieren, geben Sie im Konfigurationsmodus Folgendes ein:

Router(config)#no cache L3 bypass

Die neue Cacheeinstellung wird erst nach dem erneuten Laden des Routers wirksam.

Beim Booten des Routers werden Systeminformationen angezeigt, einschließlich Informationen zum L3-Cache. Dies liegt daran, dass die Datei startup-config noch nicht vom System verarbeitet wurde. Nach der Verarbeitung der Datei "startup-config" wird der L3-Cache umgangen, wenn der Befehl L3-Umgehung im Cache in der Konfiguration vorhanden ist.

Um die L3-Cache-Einstellung zu überprüfen, können Sie den Befehl show version ausführen. Wenn der L3-Cache umgangen wird, gibt es in der Ausgabe show version keinen Verweis auf den L3-Cache.

-

-

Eine weitere Funktion, die zur Steigerung der Systemverfügbarkeit beiträgt, ist die Cache Error Recovery Function (CERF). Wenn diese Funktion aktiviert ist (dies ist die Standardeinstellung in den neuesten Cisco IOS-Softwareversionen, aber seit Februar 2004 nur für NPE-300 und NPE-400), versucht die Cisco IOS-Software, den Paritätsfehler zu beheben und den Prozessor vor dem Absturz zu bewahren. Mit dieser Funktion werden etwa 75 % aller weichen Paritätsfehler behoben. Durch den Aufruf dieses Befehls wird die Leistung des Systems um weniger als 5 % beeinträchtigt.

CERF für NPE-300 ist in den Cisco IOS Software-Versionen 12.1(15), 12.1(12)EC, 12.0(22)S, 12.2(10)S, 12.2(10)T, 12.2(10), 12.2(2)2 zu finden. XB4, 12.2(11)BC1b und 12.1(5)XM8 oder höher

CERF für den NPE-400 finden Sie unter 12.3(3)B, 12.2(14)S3, 12.1(20)E, 12.1(19)E1, 12.3(1a), 12.2(13)T5, 12.2(18)S, 1 2.3(2)T, 12.2(18), 12.3(3) und 12.3(1)B1 oder höher.

Für CERF für NPE-300 ist die Hardware-Version 4.1 oder höher erforderlich. Um die Hardwareversion Ihres NPE-300 zu ermitteln, verwenden Sie den Befehl show c7200.

Router>show c7200 ... C7206VXR CPU EEPROM: Hardware revision 4.1 Board revision A0 ...

Für das CERF für den NPE-400 ist der Prozessor R7K Version 2.1 oder höher erforderlich. Um die Prozessorversion Ihres NPE-400 zu identifizieren, verwenden Sie den Befehl show version.

Router>show version ... cisco 7206VXR (NPE400) processor with 491520K/32768K bytes of memory. R7000 CPU at 350Mhz, Implementation 39, Rev 3.2, 256KB L2, 4096KB L3 Cache 6 slot VXR midplane, Version 2.1 ...

Hinweis: Es ist wichtig, alle relevanten Crashinfo-Dateien zu sammeln, um die Ursache des Fehlers zu ermitteln, wie in Abrufen von Informationen aus der Crashinfo-Datei erläutert.

Wenn das Problem mit den oben genannten Vorschlägen nicht behoben werden kann, kann das Ersetzen des NPE bei wiederholten Paritätsfehlern hilfreich sein, da schwere Paritätsfehler auf beschädigter Hardware zurückzuführen sind. Hardware-Ersatz ist identisch mit dem ursprünglichen NPE. Der Austausch des NPE gewährleistet nicht, dass keine weiteren Paritätsfehler auftreten, da Single Event Upsets (SEUs) in Computergeräten mit Speicher integriert sind.

Zugehörige Informationen

Revisionsverlauf

| Überarbeitung | Veröffentlichungsdatum | Kommentare |

|---|---|---|

1.0 |

13-Apr-2009 |

Erstveröffentlichung |

Cisco kontaktieren

- Eine Supportanfrage öffnen

- (Erfordert einen Cisco Servicevertrag)

Feedback

Feedback